Fターム[5F110GG24]の内容

Fターム[5F110GG24]の下位に属するFターム

1000Å(0.1μm)以下 (4,599)

Fターム[5F110GG24]に分類される特許

101 - 120 / 1,499

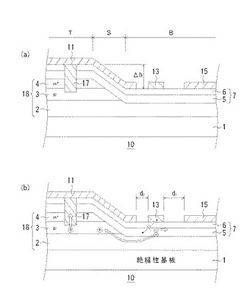

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

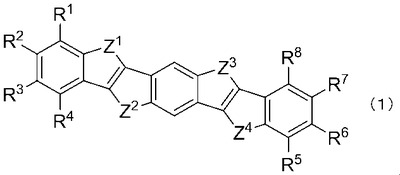

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】低コストで、後工程にて形成される上層の塗布性に優れ、かつ高信頼性を示す電界効果型トランジスタなどの提供。

【解決手段】絶縁性基板と、前記絶縁性基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成されたソース電極及びドレイン電極と、前記ゲート絶縁層上に形成され、かつ、少なくとも前記ソース電極及び前記ドレイン電極との間に形成された酸化物半導体層と、前記酸化物半導体層を被覆するように形成された保護層とを有し、前記保護層が、フッ素樹脂を含有し、前記保護層形成後の前記保護層の水に対する接触角が、75°以上90°以下である電界効果型トランジスタである。

(もっと読む)

化合物及び該化合物を用いてなる薄膜

【課題】溶媒に対する溶解性が高い化合物を提供する。

【解決手段】第1の2価の構造単位と第2の2価の構造単位とを有し、該第1の2価の構造単位がベンゼン環、シクロヘキサン環及びヘテロ原子を有する5員環あるいはベンゼン環と縮合し、シクロヘキサン環が橋架けされている特定の縮合環構造を有し、ヘテロ原子を有する5員環あるいはベンゼン環で連結する構造単位であり、該第2の2価の構造単位が、上記の構造単位とは異なる構造単位である化合物。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

真性半導体層を備えたウェーハ

【課題】ウェーハを製造するための新規な方法を提供する。

【解決手段】本発明は、ウェーハを製造するための方法に関し、この方法は、半導体基板上にドープト層を設けるステップと、ドープト層上に第1の半導体層を設けるステップと、第1の半導体層上に埋込み酸化物層を設けるステップと、埋込み酸化物層上に第2の半導体層を設けるステップと、を備える。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

キサンテン系半導体組成物

【課題】高移動度で環境安定性が高く塗布形成可能な有機半導体を提供する。

【解決手段】特定構造の縮合キサンテンコアを含む低分子半導体化合物を用いる。また、ポリマーバインダーと当該低分子半導体とを含む組成物も用いられる。この組成物から作られる半導体層は、空気中で非常に安定であり、高い移動性を有する。これらの半導体組成物は、電子機器(例えば、薄膜トランジスタ(TFT))で、半導体層のような層を作成するのに有用である。

(もっと読む)

酸化物半導体薄膜の製造方法、電界効果型トランジスタ、表示装置及びセンサ

【課題】SGZO系酸化物半導体薄膜において、低温アニールによる低抵抗化が起こらず、成膜時の抵抗値と低温アニール後の抵抗値が同等となる組成を明らかとし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した製造方法を提供する。

【解決手段】構成元素の組成比をSn:Ga:Zn=a:b:cとした場合、組成比が、a+b=2、且つ1≦a≦2、且つ1≦c≦11/2、且つc≧−7b/4+11/4を満たす酸化物半導体薄膜を基板上に成膜する成膜工程と、成膜工程後、酸化性雰囲気中で100℃以上300℃未満の熱処理を施す熱処理工程と、を有する。

(もっと読む)

薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

【課題】TFT特性が良好で表示品質や回路配線の層間絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜にコンタクトホールを開けてソース電極6s及びドレイン電極6dをソース電極接続領域及びドレイン電極接続領域に接続するとともに酸化物半導体膜上にゲート絶縁膜を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程、層間絶縁膜上に第2回路配線群19を形成する工程を有し、ゲート絶縁膜4の厚さを100nm〜500nmの範囲とし、層間絶縁膜18の厚さを1μm以上且つゲート絶縁膜4の2倍〜10倍の厚さとする。

(もっと読む)

二価結合を有する小分子チオフェン化合物を備える装置

【課題】溶液処理可能であり及び/又は周囲環境条件でよい安定性を示す小分子チオフェン化合物を備える装置を提供する。

【解決手段】多くの電極と接触している半導体層を備える電子装置であって、前記半導体層は、少なくとも1個の二価結合、及び、複数のチオフェン単位から成る小分子チオフェン化合物を含む。小分子チオフェン化合物は、化合物が、特定数(平均値でない)のチオフェン単位を持ち、少なくとも約90質量%、又は少なくとも約98質量%の純度を有する。

(もっと読む)

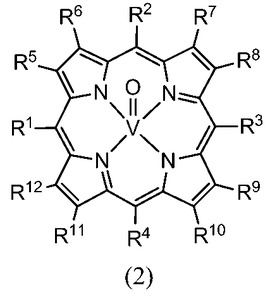

テトラビシクロポルフィリンバナジル錯体の製造方法、半導体層形成用組成物、電子デバイスの製造方法、太陽電池及び太陽電池モジュール

【課題】電子デバイスで好適に用いられるテトラベンゾポルフィリンバナジル錯体の高純度製造法の提供。

【解決手段】テトラビシクロポルフィリン化合物とバナジル化合物の反応を65℃以上95℃以下の温度で行う。式(2)の錯体の製造方法。 (もっと読む)

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

有機半導体としてのアザペリレン類

【課題】有機半導体材料として使用できるアザペリレン化合物の提供。

【解決手段】下記一般式(I)で表されるアザペリレン化合物。

(式中、R1、R2、R3及びR4のそれぞれは、独立して、H、非置換又は置換されているアルキル、非置換又は置換されているアルケニル、非置換又は置換されているアルキニル、非置換又は置換されているアリール、ハロゲン、Si(RH)3、XR6から選択されるか、R1とR2、R2とR3、R3とR4の一つ以上が、それらが結合する炭素原子と一緒になって、飽和又は不飽和の、非置換又は置換されている炭素環又は複素環を形成する。)

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】本発明は、良質な酸化物半導体のチャネル領域と、チャネル領域の抵抗率よりも低い抵抗率でソース・ドレイン領域にも適用可能な低抵抗領域とが形成され、オン電流、キャリア移動度及び信頼性が高く、ヒステリシス性が小さい良好な電気特性を、工程数を増やすことなく実現できる半導体デバイス及びその製造方法を提供することを目的とする。

【解決手段】酸化物半導体をチャネル材料に用いた半導体デバイスの製造方法であって、

薄膜領域21と、該薄膜領域よりも膜厚の厚い厚膜領域22、23とを有する酸化物半導体膜20を形成する工程と、

前記酸化物半導体膜にエネルギービームを照射し、前記薄膜領域と前記厚膜領域の抵抗率を膜厚に応じて変化させる工程と、

前記薄膜領域をチャネル領域21aとし、前記厚膜領域を低抵抗領域22a、23aとして前記半導体デバイスを形成する工程と、を有することを特徴とする。

(もっと読む)

101 - 120 / 1,499

[ Back to top ]