Fターム[5F110GG24]の内容

Fターム[5F110GG24]の下位に属するFターム

1000Å(0.1μm)以下 (4,599)

Fターム[5F110GG24]に分類される特許

121 - 140 / 1,499

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能であり、有機溶媒への溶解性にも優れる含窒素縮合環化合物を提供すること。

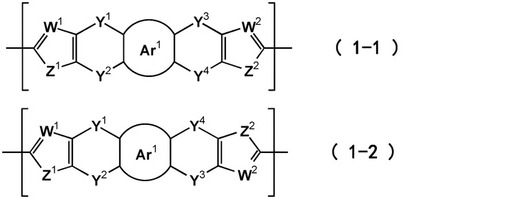

【解決手段】式(1−1)又は式(1−2)で表される構造単位を有する含窒素縮合環化合物。 (もっと読む)

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

ジカルコゲノベンゾジピロール化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】キャリア移動度がさらに向上した有機半導体デバイス、該デバイスに含まれる薄膜及び該薄膜に含まれる化合物が求められていた。

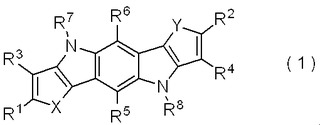

【解決手段】式(1)

(式中、X及びYは、それぞれ独立して、硫黄原子、酸素原子、セレン原子、テルル原子、及びSO2を表す。R1〜R8は、それぞれ独立して、水素原子、ハロゲン原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜30のアリール基又は炭素数4〜30のヘテロアリール基を表す。)

で表されるジカルコゲノベンゾジピロール化合物。

(もっと読む)

半導体装置

【課題】消費電力を極力抑制することで電源の安定化を実現する半導体装置を提供する。

【解決手段】ロジック部11、メモリ部12、ロジック部とメモリ部の一方又は両方の動作頻度を検出する検出部13、検出部の検出結果に基づきロジック部及びメモリ部の一方又は両方にしきい値制御信号を供給するしきい値制御部14を有する半導体装置である。ロジック部とメモリ部の各々は複数のトランジスタを有しており、複数のトランジスタの各々は、論理信号が入力される第1のゲート電極と、しきい値制御信号が入力される第2のゲート電極と、半導体膜とを有する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体組成物

【課題】高い電界効果移動度、空気安定性および良好な溶解性を示す半導体化合物の提供。

【解決手段】下式に代表される化合物: (もっと読む)

(もっと読む)

半導体化合物

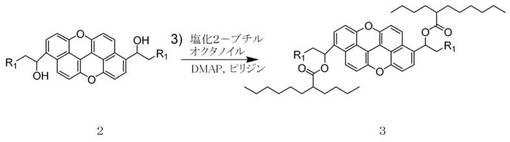

【課題】空気安定性、良好な溶解度、および高い移動度を持つ有機薄膜トランジスタ用半導体を提供する。

【解決手段】特定構造のチアキサンテノチアキサンテン化合物を活性層として用いる。チアキサンテノチアキサンテン化合物は主に結晶性または液晶である。この化合物は、空気安定性、良好な溶解度、および高い移動度を確実にするように設計される。有機薄膜トランジスタは一般に、基板20上に、ゲート電極30、ソース電極50およびドレイン電極60、ゲート電極をソースおよびドレイン電極と分離する電気絶縁ゲート誘電体層40、およびゲート誘電体層と接触し、ソースおよびドレイン電極を架橋する半導体層70を含む。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの活性層に好適に用いられる非晶質酸化物の製造方法を提供する。

【解決手段】基板1上に、非晶質酸化物層2を形成する前に、基板1表面にオゾン雰囲気中で紫外線を照射したり、基板1表面にプラズマを照射したり、あるいは基板1表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物層2を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板1上に、非晶質酸化物層2を形成する後に、非晶質酸化物層2の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

薄膜トランジスタ用ゲート絶縁膜および該絶縁膜を備えた薄膜トランジスタ素子

【課題】低温条件下かつ溶液塗布プロセスにより形成可能であり、薄膜トランジスタにおける電気特性であるヒステリシス、On/Off比が良好な薄膜トランジスタ用ゲート絶縁膜及び該絶縁膜を備えた薄膜トランジスタを提供する。

【解決手段】必須成分として(A)アルケニル基を有する化合物、(B)SiH基を有する化合物、(C)ヒドロシリル化触媒を含有する硬化性組成物を低温条件下によるポストベイクしたゲート絶縁膜を用いることにより、良好なトランジスタ特性が発現する。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体層とする薄膜トランジスタ

を有する半導体装置の作製方法において、酸化物半導体層に接する酸化物絶縁膜を形成す

る。酸化物半導体層を減圧されたチャンバー内に導入後、窒素雰囲気下で加熱処理工程、

プラズマ(少なくとも酸素プラズマを含む)の導入工程を行い、成膜ガスを導入して酸化

物絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

電荷輸送膜、有機電子デバイス、電子写真感光体、プロセスカートリッジ、及び画像形成装置

【課題】可とう性及び靭性に優れた最表面層を持つ電荷輸送膜を提供すること

【解決手段】電荷輸送性骨格を持つエンチオール樹脂を含んで構成され、且つ硫黄原子の含有率が2.0質量%以上15質量%以下である電荷輸送膜である。

(もっと読む)

121 - 140 / 1,499

[ Back to top ]