Fターム[5F110GG24]の内容

Fターム[5F110GG24]の下位に属するFターム

1000Å(0.1μm)以下 (4,599)

Fターム[5F110GG24]に分類される特許

161 - 180 / 1,499

誘電性組成物

【課題】電子機器(例えば、薄膜トランジスタ)は、基板と、誘電性組成物から作られた誘電層とを備える。薄く、平滑で、ピンホールを含まないゲート誘電層を提供する。

【解決手段】誘電性組成物は、誘電性材料と、低表面張力添加剤とを含む。低表面張力添加剤によって、ピンホールが少なく、機器の収量が大きい、薄い平坦な誘電層を作成することができる。特定の実施形態では、誘電性材料は、低k誘電性材料と、高k誘電性材料とを含む。堆積したら、低k誘電性材料と高k誘電性材料とは、別個の相を形成する。

(もっと読む)

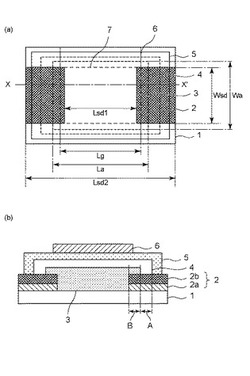

薄膜トランジスタ

【課題】 結晶性に優れ、電気特性、特にリーク電流の少ない結晶性シリコン薄膜半導体装置を提供する。

【解決手段】 ソース電極およびドレイン電極上に非晶質シリコン層を形成し、その上に微結晶シリコン層、ゲート絶縁層、ゲート電極を形成する薄膜トランジスタであって、前記非晶質シリコン層と前記ソース電極とドレイン電極とが前記微結晶シリコン層を介して接続する領域と、前記非晶質シリコン層と前記ソース電極およびドレイン電極と直接接続する領域と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

半導体装置及び表示装置

【課題】高融点メタルバリア層を有していなくても、高温熱処理後の電気特性を良好にする技術を提供することを目的とする。

【解決手段】半導体装置は、透明絶縁性基板1上に形成されたゲート電極2と、ゲート電極2上にゲート絶縁膜6を介して順次に形成されたSi半導体能動膜7と、n型の導電型を有するオーミック低抵抗Si膜8とを含む半導体層51と、半導体層51と直接接合された、少なくともアルミニウム(Al)を含むソース・ドレイン電極9,10とを備える。半導体層51は、平面視においてゲート電極2の外周よりも内側に形成され、Si半導体能動膜7の側面とソース・ドレイン電極9,10との界面近傍である第1領域には、少なくとも窒素(N)が含まれる。

(もっと読む)

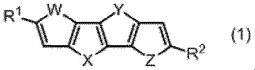

置換カルコゲノアセン化合物及び該化合物を含有する有機半導体デバイス

【課題】有機半導体デバイスに用いることのできる置換カルコゲノアセン化合物を提供するとともに、該化合物を用いた、キャリア電界効果移動度が十分な有機半導体デバイスを提供する。

【解決手段】式(1)で表される置換カルコゲノアセン化合物。

(式中、

W、X、Y及びZは、酸素原子、硫黄原子、セレン原子又はテルル原子を表す。

R1及びR2は、炭素数1〜30のフッ素原子を有していてもよいアルキル基、炭素数1〜30のフッ素原子を有していてもよいアルコキシ基、炭素数1〜30のフッ素原子を有していてもよいアルキルチオ基、炭素数2〜30のフッ素原子を有していてもよいアルキニル基、炭素数7〜36のフッ素原子を有していてもよいアリール基又は炭素数5〜34のフッ素原子を有していてもよいヘテロアリール基を表す。)

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

錫を含む非晶質酸化物薄膜、及び薄膜トランジスタ

【課題】トランジスタ特性が良好で、ディスプレイパネルに適した電界効果トランジスタを提供する。

【解決手段】少なくとも錫(Sn)を含み、SnOとSnO2の合計を100モル%としたときのSnOの割合が30モル%未満である非晶質酸化物薄膜。

(もっと読む)

エッジエミッティングレーザのモノリシックアレイ

【課題】相分離誘電体構造を備える電子デバイスの製造方法を提供する。

【解決手段】本製造方法は、半導体層を堆積し、低誘電率材料、高誘電率材料及び液体を含む誘電体組成物を低誘電率材料及び高誘電率材料を相分離させずに液相堆積し、低誘電率材料および高誘電率材料の相分離を生成することを含む。低誘電率材料は半導体層に最も近い誘電体構造の領域内の高誘電率材料の濃度に比べて高濃度であり、半導体層の堆積は、誘電体組成物を液相堆積する前、または相分離を生成した後になされる。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

半導体薄膜、薄膜トランジスタ及びその製造方法

【課題】耐還元性に優れた半導体薄膜及びその製造方法、チャネル層上に酸素透過性膜等のバッファー層を設けなくても安定したTFT特性が得られる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】1種以上のアモルファス金属酸化物を含有し、前記金属酸化物の少なくとも一部の金属原子にOH基が結合している半導体薄膜。

(もっと読む)

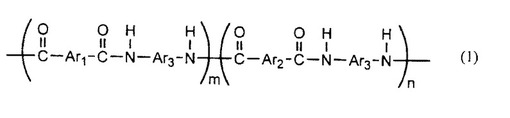

フェノール性水酸基含有芳香族ポリアミド樹脂を含有する絶縁層を有する有機半導体素子並びにその製造方法

【課題】本発明のフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を用いた有機半導体素子は、トランジスタ特性及び耐湿熱性等の耐久性に優れており、実用性の高い有機半導体素子を提供する。

【解決手段】下記式(1)で表されるフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を有する有機半導体素子。

(式(1)中、各構造単位の平均重合度m及びnはm+n=2〜200であり、Ar1及びAr3は2価の芳香族基、Ar2はフェノール性水酸基を有する2価の芳香族基を表す。)

(もっと読む)

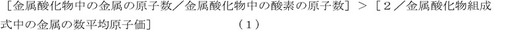

金属酸化物半導体薄膜

【課題】移動度が高く電気的特性に優れ、印刷法でも製造可能な金属酸化物半導体薄膜を提供する。更に、本発明は、該金属酸化物半導体薄膜の製造方法及び該金属酸化物半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】金属酸化物を含有する金属酸化物半導体薄膜であって、前記金属酸化物は、下記式(1)に規定する関係を満たすことを特徴とする金属酸化物半導体薄膜。

[数1] (もっと読む)

(もっと読む)

半導体装置、パワーダイオード及び整流器

【課題】高耐圧、低逆方向飽和電流、高いオン電流などの電気特性を有する半導体装置を提供することである。なかでも、非線形素子より構成されるパワーダイオード及び整流器を提供することである。

【解決手段】第1の電極と、第1の電極を覆うゲート絶縁層と、ゲート絶縁層と接して且つ第1の電極と重畳する酸化物半導体層と、酸化物半導体層の端部を覆う一対の第2の電極と、一対の第2の電極及び酸化物半導体層を覆う絶縁層と、絶縁層に接して且つ一対の第2の電極の間に設けられる第3の電極と、を有し、一対の第2の電極は酸化物半導体層の端面に接する半導体装置である。

(もっと読む)

薄膜トランジスタ

【課題】電気特性の変動が少なく、信頼性の高いトランジスタを提供する。また、電気特性の変動が少なく、信頼性の高いトランジスタを、生産性高く作製する。また、経年変化の少ない表示装置を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース領域及びドレイン領域として機能する不純物半導体膜との間に、微結晶半導体領域及び一対の非晶質半導体領域を有する半導体積層体を有し、微結晶半導体領域は、ゲート絶縁膜側の窒素濃度が少なく、非晶質半導体に接する領域の窒素濃度が高く、且つ非晶質半導体との界面が凹凸状である。

(もっと読む)

半導体装置

【課題】本発明は、移動度が向上し、コンタクト抵抗が低減された半導体装置を提供する。

【解決手段】基板11上にゲート電極12、ゲート絶縁膜13、ソース・ドレイン電極14および有機半導体15がこの順に積層された半導体装置において、有機半導体層15は、第1の層15aと第1の層15aよりもグレインサイズの小さい第2の層15bとを備えており、第1の層15aがゲート絶縁膜13側に配置されていることを特徴とする半導体装置である。

(もっと読む)

表示装置、及び、その製造方法

【課題】薄膜トランジスタにおいて生じるリーク電流を抑えつつ、表示装置の生産性を向上させることを目的とする。

【解決手段】基板301と、基板301に形成されている複数の薄膜トランジスタTFTと、を有する表示装置であって、薄膜トランジスタTFTは、ゲート電極303と、ゲート電極303の上側に配置される微結晶半導体層305と、微結晶半導体層305上に配置される非晶質半導体層306と、を有し、非晶質半導体層306の水素濃度が、12atom%以下である、ことを特徴とする表示装置。

(もっと読む)

液晶表示装置

【課題】画素内におけるTFTのON電流を増大させ、かつ、ON電流のばらつきを抑える。

【解決手段】TFTにおける半導体層103と1層目のn+a−Si層14をプラズマCVDによって連続して形成する。半導体層103と1層目のn+a−Si層104を同時にパターニングする。その後、2層目のn+a−Si層105を1層目のn+a−Si層104の上と、半導体層103の側部を覆うように形成する。半導体層103の上に連続して1層目のn+a−Si層104を形成することによってTFTのON電流を増大させることが出来るとともに、ON電流のばらつきを小さくすることが出来る。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

161 - 180 / 1,499

[ Back to top ]