Fターム[5F110GG24]の内容

Fターム[5F110GG24]の下位に属するFターム

1000Å(0.1μm)以下 (4,599)

Fターム[5F110GG24]に分類される特許

141 - 160 / 1,499

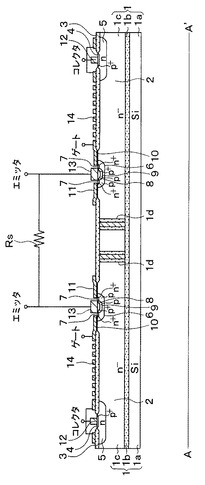

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

電荷輸送膜、有機電子デバイス、電子写真感光体、プロセスカートリッジ、及び画像形成装置

【課題】可とう性及び靭性に優れた最表面層を持つ電荷輸送膜を提供すること

【解決手段】電荷輸送性骨格を持つエンチオール樹脂を含んで構成され、且つ硫黄原子の含有率が2.0質量%以上15質量%以下である電荷輸送膜である。

(もっと読む)

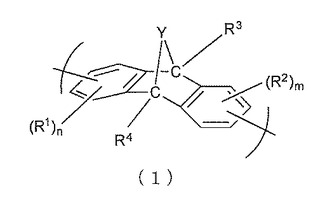

有機トランジスタの製造方法

【課題】電界効果移動度が高い有機トランジスタを製造する方法を提供すること。

【解決手段】式

[式中、R1及びR2は、それぞれ独立に、置換基を表す。R3及びR4は、それぞれ独立に、水素原子又は置換基を表す。n及びmは、それぞれ独立に、0〜3の整数を表す。Yは、2価の基を表す。R1が複数個ある場合、及びR2が複数個ある場合、それらは同一でも相異なってもよい。]で表される構造単位を含む化合物を含有する有機膜を形成する工程と、Yで表される2価の基の少なくとも一部を脱離させて、有機半導体層を製造する工程とを、有する、ゲート電極、ソース電極、ドレイン電極及び有機半導体層を有する有機トランジスタの製造方法。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

薄膜半導体デバイスおよび薄膜半導体デバイスの製法

【課題】安価に、デバイスの効率および長期間安定性が改善された薄膜半導体デバイスを提供する。

【解決手段】薄膜半導体デバイスは、セルロースを含む材料、より具体的には、紙シート材料の基材および基材上の層に蒸着された無機材料の多数の薄膜層を含み、無機材料の多数の薄膜層のうち少なくとも一つは、該基材または基礎をなす無機材料の薄膜層の一方に印刷され、無機材料の多数の薄膜層のうちの少なくとも一つはナノ結晶シリコン粉末を含む活性半導体層およびポリマーを含む担体を含む。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】新規なp型酸化物半導体を活性層に用いた電界効果型トランジスタなどの提供。

【解決手段】ゲート電圧を印加するためのゲート電極と、電流を取り出すためのソース電極及びドレイン電極と、前記ソース電極及び前記ドレイン電極との間に形成されたp型酸化物半導体からなる活性層と、前記ゲート電極と前記活性層との間に形成されたゲート絶縁層とを有し、前記p型酸化物半導体が、一般式ABO3(Aは、Sr及びBaの少なくともいずれかを含む。Bは少なくともBiを含む。)で表され、かつ擬ペロブスカイト構造である電界効果型トランジスタである。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。また、本発明の目的は、基材がポリマー材料を有する半導体積層体を提供することである。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

光電変換素子、光電変換回路及び表示装置

【課題】赤外光及び可視光に対する感度の高い光電変換素子を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆う第1のゲート絶縁層と、第1のゲート絶縁層上の結晶性半導体層と、結晶性半導体層上の非晶質半導体層と、非晶質半導体層上の不純物半導体層と、不純物半導体層に接するソース電極及びドレイン電極と、少なくともソース電極及びドレイン電極の間を覆う第2のゲート絶縁層と、第2のゲート絶縁層上の第2のゲート電極と、を有し、少なくともソース電極とドレイン電極の間に受光部が設けられ、第1のゲート電極は遮光性材料により結晶性半導体層及び非晶質半導体層のすべてと重畳し、第2のゲート電極は透光性材料により受光部と重畳し、第1のゲート電極は、ソース電極またはドレイン電極に電気的に接続されている光電変換素子を提供する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体組成物

【課題】高い移動度と優れた安定性をもつ半導体組成物と、それを使った電子機器の製造プロセスを提供する。

【解決手段】半導体組成物は、ポリマーバインダーと、下式の低分子半導体とを含む。

式中、R1は、アルキル、アルケニル、アルキニル、アリール、ヘテロアリール、アルコキシ、トリアルキルシリル、ケトニル、シアノ、ハロゲン等であり、m、nは、0〜6であり、Xは、O、S、Seから選択され、a、b、cは、0または1である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜をチャネルに用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】加熱処理により第1の結晶構造となりうる酸化物半導体膜と、加熱処理により第2の結晶構造となりうる酸化物半導体膜を積層して形成し、その後加熱処理を行うことによって、第2の結晶構造を有する酸化物半導体膜を種として第1の結晶構造を有する酸化物半導体膜へ結晶成長する。このようにして形成した酸化物半導体膜を、トランジスタの活性層に用いる。

(もっと読む)

半導体装置

【課題】光感度を向上させた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、柔軟性を有し、可視光に対して透明な透明基板12と、透明基板上に設けられる透明電極14と、透明電極の透明基板と接している面の反対側の一部に設けられる有機半導体層16と、有機半導体層の透明電極と接している面の反対側の表面の上方に設けられる反射層71とを備える。

(もっと読む)

アクティブマトリックス基板、及び液晶装置

【課題】TFTの光リーク電流が低減され、かつ、従来よりも少ないフォトリソフォグラフィ工程で製造することが可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板201は、絶縁性基板1上に、基板1側から、ゲート電極2と、ゲート電極2を覆うゲート絶縁膜6と、互いに離間形成されたドレイン電極9及びソース電極11と、チャネル層を含む少なくとも1層の半導体膜21とが順次形成された薄膜トランジスタ101と、画素電極10とが複数対アレイ状に形成されたものである。ドレイン電極9及びソース電極11は、基板1側から透光性導電膜EM2と非透光性導電膜EM3とが順次積層された積層構造を有し、かつ、ドレイン電極9の透光性導電膜EM2及び/又は非透光性導電膜EM3が延設され、この延設部分により画素電極10が形成されたものである。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】高い表示品質を実現することができるTFT、アクティブマトリクス基板及びそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2aと、ゲート電極2aを覆うように設けられたゲート絶縁膜3と、ゲート絶縁膜3の上に設けられ、ゲート電極の上方に配置された半導体膜5と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたソース電極7と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたドレイン電極9と、ソース電極7又はドレイン電極9の少なくとも一方とゲート絶縁膜3との間に設けられ、半導体膜5と分離して配置された低反射膜6と、を備え、低反射膜6が、平面視におけるゲート電極2aの外側において、ソース電極7、ドレイン電極9のパターンと略同一形状、又は、はみ出しているものである。

(もっと読む)

141 - 160 / 1,499

[ Back to top ]