Fターム[5F110GG37]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物の分布 (414) | 一導電型不純物のみ (175)

Fターム[5F110GG37]に分類される特許

1 - 20 / 175

半導体装置およびその製造方法

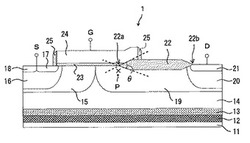

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

半導体装置

【課題】インバータ回路を構成する直列接続された素子を備えた半導体装置において、その直列接続の高電位配線の影響による耐圧低下が生じるのを防止する半導体装置の提供。

【解決手段】第1および第2の素子は、各々、電流のスイッチングを行うトランジスタと、還流を行うダイオードとを含み、かつ、トランジスタの第1主電極とダイオードの第1主電極が電気的に接続され、トランジスタの第2主電極とダイオードの第2主電極が電気的に接続され、第1の素子および第2の素子は、第1の素子におけるトランジスタの第1主電極と、第2の素子におけるトランジスタの第2主電極が電気的に接続され、かつ、半導体基板を平面視したときに、第1の素子におけるトランジスタの第1主電極とドリフト領域の間の導電性半導体領域と、第2の素子におけるトランジスタの第2主電極とドリフト領域の間の導電性半導体領域とが対向するように、配置されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

横型IGBT

【課題】薄い活性層を有する積層基板に形成される横型IGBTの特性を改善する。

【解決手段】横型IGBT1は、p型のコレクタ領域46,48とp型のコレクタウェル領域44を備えている。コレクタウェル領域44は、コレクタ領域46,48を取り囲んでコレクタ領域46,48に接している。コレクタウェル領域44の不純物濃度は、コレクタ領域46,48の不純物濃度よりも薄い。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置

【課題】バンド間トンネリングが横方向に起こる構造を有し、バンド間トンネリングが起こる領域が大きいトンネルトランジスタを備える半導体装置を提供する。

【解決手段】第1上面S1と、第1上面S1よりも高さの低い第2上面S2と、第1上面と第2上面との間に存在する段差側面S3と、を有する段差が形成された基板。さらに、基板の段差側面S3と第2上面S2とに連続して形成されたゲート絶縁膜と、基板の段差側面S3に形成されたゲート絶縁膜に接するよう、第2上面S2上にゲート絶縁膜131を介して形成されたゲート電極132とを備える。さらに、基板内において、第1上面の下方に形成された第1導電型のソース領域121と、第2上面の下方に形成された第2導電型のドレイン領域122と、段差側面S3とソース領域122との間に形成された第2導電型の側方拡散領域123とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 p型ウェル領域形成のための熱拡散時間の増大を抑え、短時間で容易に製造することのできる半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板1と前記半導体基板1上に絶縁膜2を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性層3内に、第2導電型の半導体層からなるウェル(ここではp型ウェル領域4)を形成するとともに、ウェル内および第1導電型の活性層3内に、第1導電型の半導体層からなるソースおよびドレイン領域を形成した横型MOSFETの製造方法であって、SOI基板の第1の半導体層の膜厚dを決定する工程が、チャネル長Lchのn倍以下となるようにする工程であり、熱拡散雰囲気下における第2導電型の半導体層を構成する不純物の、第1導電型の半導体層中における水平方向の拡散速度をVdifh、垂直方向の拡散速度をVdifvとしたとき、

このnは、

n=Vdifv/Vdifh

d/Lch<n

を満たすように選択される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

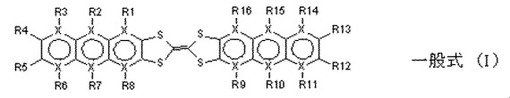

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

電気光学装置の製造方法

【課題】液晶装置等の電気光学装置において、高品質な表示を行う。

【解決手段】電気光学装置の製造方法は、基板(10)に、トランジスタの半導体層(1a)を形成する半導体層形成工程と、半導体層のチャネル部(1a’)に不純物を導入する不純物導入工程と、基板を平面的に見て、チャネル部に重なるようにゲート電極(3b)を形成するゲート電極形成工程とを備える。不純物導入工程においては、不純物は、チャネル幅方向においてチャネル部の端部に位置する第1領域、及びチャネル長方向において第1領域よりも幅が狭いチャネル部の第2領域にそれぞれ導入される。

(もっと読む)

半導体装置の製造方法

【課題】寄生MOSの形成を抑制し、且つ狭チャネル化を低減した半導体装置の製造方法を提供する。

【解決手段】支持基板2と絶縁層3と半導体層4とを含むSOI基板1に、ソース領域及びドレイン領域が第1導電型であるトランジスターを形成する半導体装置の製造方法であって、半導体層4上に、第1の耐酸化性膜6a’を形成する工程と、第1の耐酸化性膜6a’をマスクにして、第1導電型とは導電性の異なる、第2導電型の不純物7を半導体層4に注入する工程と、第2導電型の不純物7を半導体層4に注入する工程の後、第1の耐酸化性膜6a’の側面に第2の耐酸化性膜6b’を形成する工程と、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’をマスクにして、素子分離層8を形成する工程と、素子分離層8を形成する工程の後、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’を半導体層4上から除去する工程とを有することを特徴とする半導体装置100の製造方法。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

1 - 20 / 175

[ Back to top ]