Fターム[5F110HK02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241)

Fターム[5F110HK02]の下位に属するFターム

Al (3,898)

高融点金属 (4,055)

シリサイド (1,278)

合金 (2,248)

透明導電膜(例;ITO) (2,330)

Fターム[5F110HK02]に分類される特許

101 - 120 / 4,432

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、並びに電気泳動ディスプレイ

【課題】画素電極間の距離が大きくて印刷に適し、しかも画素電極間の距離が大きい場合でも所望の表示を行うことができること。

【解決手段】薄膜トランジスタアレイは、絶縁基板1上に、少なくともゲート電極2と、ゲート絶縁膜3と、ソース電極4と、ドレイン電極5と、前記ドレイン電極5に接続された画素電極9と、ソース電極4とドレイン電極5との間に形成された半導体層6と、を有する薄膜トランジスタを、複数のゲート電極2がゲート配線2aに接続され、複数のソース電極4がソース配線4aに接続された状態でマトリクス状に配置した薄膜トランジスタアレイであって、隣り合う画素電極9の間の部分を線とし、複数の前記線が交わる部分を節として表したときに、画素電極9の配置が、1つの前記節に3本の前記線がつながる配置となる。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

有機半導体装置の製造方法

【課題】塗布開始場所以外の場所からの結晶成長を防止し、配向度の高い有機半導体薄膜を形成できるようにする。

【解決手段】有機半導体材料を含むインク11の塗布開始場所からインク11を乾燥させ、インク11中の有機半導体材料を結晶化させて有機半導体薄膜15を形成する。このとき、ノズル部2として、基板12の表面と対向する先端面2fを構成するオーバハング部を有したノズル胴体部2aと、ノズル胴体部2aの先端面2fから基板12側に突出すると共に一方向を長手方向として延設された吐出口2gを有する溶液吐出部2cとを備えたものを用いる。そして、溶液吐出部2cの下端を基板12から離間させた状態でインク11を吐出し、吐出されたインク11にて溶液吐出部2cと基板12の間に液溜まりを形成しつつ、ノズル部2を吐出口2gの長手方向に対する垂直方向に移動させることによりインク11をライン状に塗布する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】印刷法を用いて薄膜トランジスタを製造する場合において、前処理などを必要とせずに微細パターンを形成可能であり、トランジスタ特性の面内均一性に優れるとともに、インキの利用効率に優れた薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性の基板上に形成されたゲート電極41、ゲート絶縁膜、ソース電極43、ドレイン電極44、半導体層45及び封止層46を有する薄膜トランジスタ1を製造する薄膜トランジスタの製造方法であって、インキ供給手段を用いて凹凸パターンが形成された印刷用版にインキを供給するインキ供給工程と、インキの予備乾燥を経た後に凸版を用いて非画線部のインキ液膜を除去するインキ液膜除去工程と、印刷用版上に残った画線部のインキ液膜を基板40に転写して、半導体層45及び封止層46のうち少なくとも一方を形成するインキ液膜転写工程を有する。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

薄膜トランジスタアレイ、薄膜トランジスタアレイの製造方法、画像表示装置

【課題】高開口率を得るために形成する層間絶縁膜のパターニング性、歩留まりを向上させ、生産性に優れた薄膜トランジスタアレイを提供する。

【解決手段】ゲート絶縁膜2上には、ゲート電極11に重なる位置に、ドレイン電極16と、ソース電極17と、を隔てて設けてあり、ドレイン電極16には、画素電極15を接続し、ソース電極17には、ソース配線18を接続してある。また、ゲート絶縁膜2上には、ドレイン電極16及びソース電極17の双方に重なるように、半導体層3を設けてある。ゲート絶縁膜2上には、画素電極15の一部を露出させた状態で、ソース電極17、ソース配線18、ドレイン電極16、画素電極15、半導体層3を封止する一層目封止層4を設け、一層目封止層4上には、ソース電極17及びソース配線18に重なる位置に、二層目封止層5を設けてある。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

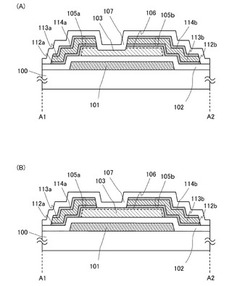

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】高い移動度を実現でき、且つ、ストレス耐性(ストレス印加前後のしきい値電圧シフト量が少ないこと)にも優れた薄膜トランジスタ用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、Zn、Sn、およびInと;Si、Hf、Ga、Al、Ni、Ge、Ta、W、およびNbよりなるX群から選択される少なくとも一種の元素(X群元素)と、を含むものである。

(もっと読む)

Cu−Mn合金スパッタリングターゲット材、それを用いた薄膜トランジスタ配線及び薄膜トランジスタ

【課題】高いバリア性を有するCu−Mn合金膜を形成する。

【解決手段】半導体素子の配線の形成に用いられるCu−Mn合金スパッタリングターゲット材10であって、濃度が8原子%以上30原子%以下のMnと、不可避的不純物とを含むCu−Mn合金からなり、Cu−Mn合金の平均結晶粒径が10μm以上50μm以下である。

(もっと読む)

スイッチング素子及びその製造方法

【課題】CNTとゲート絶縁膜との相互作用を高め、良好かつ安定したトランジスタ特性を示すスイッチング素子を提供する。

【解決手段】本発明のスイッチング素子は、ゲート絶縁膜と、前記ゲート絶縁膜に接して形成された活性層とを具備する。前記活性層は、カーボンナノチューブを含み、前記ゲート絶縁膜は、側鎖に芳香族環を有する非共役高分子を含んでいる。

(もっと読む)

酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板

【課題】理論的根拠に基づいて酸化物半導体の母材料に添加される物質を使用することによって、優れた特性を有する酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板を提供する。

【解決手段】 本発明の一実施形態に係る酸化物半導体は、亜鉛(Zn)及び錫(Sn)のうちの少なくとも一つの元素を含む第1物質、及び前記第1物質に添加される第2物質を含み、前記第1物質と酸素(O)との電気陰性度差値から前記第2物質と酸素(O)との電気陰性度差値を引いた値が1.3以下であることを特徴とする。

(もっと読む)

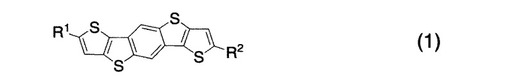

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

トランジスタおよびその製造方法、並びに表示装置

【課題】良好な特性を有するトランジスタおよびその製造方法、並びにそのトランジスタを備えた表示装置を提供する

【解決手段】制御電極と、制御電極に対向する能動層と、能動層に電気的に接続された第1電極および第2電極と、制御電極と第1電極および第2電極との間に設けられ、ジアリルイソフタレート樹脂を含有する絶縁層とを備えたトランジスタ。

(もっと読む)

101 - 120 / 4,432

[ Back to top ]