Fターム[5F110HK02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241)

Fターム[5F110HK02]の下位に属するFターム

Al (3,898)

高融点金属 (4,055)

シリサイド (1,278)

合金 (2,248)

透明導電膜(例;ITO) (2,330)

Fターム[5F110HK02]に分類される特許

161 - 180 / 4,432

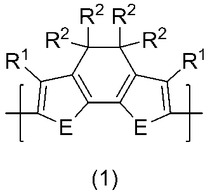

高分子化合物及びそれを用いた有機トランジスタ

【課題】有機トランジスタの活性層に用いた場合に、電界効果移動度が十分に高くなる高分子化合物を提供する。

【解決手段】式

〔式中、Eは、−O−、−S−又は−Se−を表す。R1は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基又はハロゲン原子を表す。R2は、水素原子、アルキル基、アリール基、ヘテロアリール基又はハロゲン原子を表すか、2個のR2が連結して環を形成する。〕で表される構造単位と、式(1)で表される構造単位とは異なる式−Ar1−で表される構造単位とを含む高分子化合物である(式中、Ar1は、2価の芳香族基、−CR3=CR3−で表される基又は−C≡C−で表される基を表す)。

(もっと読む)

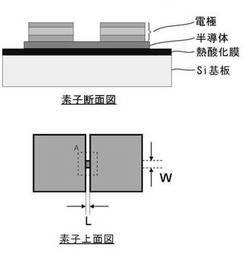

電界効果素子

【課題】高移動度、高オン・オフ比の電界効果素子を提供する。

【解決手段】絶縁膜層、前記絶縁膜層上に積層されたチャネル層、及び電極としてゲート電極、ソース電極及びドレイン電極の3つを有する電界効果素子であって、前記チャネル層は表面粗さ0.2nm以上1.3nm以下であり、前記チャネル層はIn,Ga,Sn及びZnから選択される1以上の元素を含有する非晶質酸化物半導体からなる電界効果素子。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

液晶表示装置

【課題】オフリーク電流を抑制することが可能な液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置では、半導体層53は、平面視においてゲート電極51の範囲内に配置される。ソース電極55及びドレイン電極57は、平面視において半導体層53の範囲内に配置される。シールド7は、保護絶縁膜4上に配置され、画素電極6と同一の材料からなり、画素電極6と電気的に接続されていない。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

液晶表示装置

【課題】部材を新たに追加することなく、偏光サングラスを装着したままランドスケープ、ポートレートともに表示が観察可能な表示品位の優れたFFSモードの液晶表示装置を提供すること。

【解決手段】本発明に係る液晶表示装置は、ゲート配線43の延在方向に対して0°<α<90°の角度αで傾斜した配向方向を有する配向膜と、画素電極6と、画素電極6上に絶縁膜を介して対向配置される共通電極8と、共通電極8に形成され、画素電極6との間で液晶20にフリンジ電界を発生させるスリットとを備える。画素内は、配向方向に延在する境界線により分割され、スリットは、各領域において境界線の延在する方向に対して角度±θ傾斜して配置された複数の第1スリットA、第2スリットBと、境界線上に形成され、該境界線に沿う方向に延在する端辺を有する第3スリットCを有し、第2の基板には配向方向に設定された吸収軸を有する偏光板を有する。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に接続するソース電極層またはドレイン電極層との接触抵抗の低減を図る。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層のうち、酸化物半導体層と接する一層104a、104bを薄いインジウム層または薄いインジウム合金層とする。なお、酸化物半導体層103は、インジウムを含む。二層目以降のソース電極層105aまたはドレイン電極層105bの材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】絶縁層上の有機半導体層をレーザ光を用いてパターニングしたときであっても、有機半導体層に損傷が生じ難い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(A)基体10上にゲート電極12を形成した後、(B)基体10及びゲート電極12上にゲート絶縁層13を形成し、次いで、(C)基体10に到達する分離溝16をゲート絶縁層13に形成した後、(D)ゲート絶縁層13上及び分離溝16の底部に露出した基体10上に有機半導体層14を形成し、次に、(E)少なくとも分離溝16の底部に露出した基体10上に形成された有機半導体層14の部分にレーザ光を照射して分離溝16の底部の少なくとも一部を露出させる一方、有機半導体層14の上に一対のソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

表示装置およびその製造方法

【課題】活性層となる酸化物導電体層への光の入射を防ぎ、TFT特性の低下を抑制することが可能な表示装置およびその製造方法を提供する。

【解決手段】本技術の表示装置は、活性層が酸化物導電体よりなる薄膜トランジスタと、薄膜トランジスタ上に設けられた発光素子と、薄膜トランジスタおよび発光素子の各端面、並びに発光素子の上面の一部を覆う遮光膜とを備える。

(もっと読む)

電子装置

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

電子機器および半導体基板

【課題】有機半導体層の電気的特性を確保することが可能な電子機器を提供する。

【解決手段】電子機器は、光源と、有機半導体層を含む薄膜トランジスタと、光源から生じた光が有機半導体層に至る経路に配置され、その有機半導体層の光吸収波長域のうちの少なくとも一部を含む波長域の光を吸収すると共にそれ以外の波長域の光を透過する光吸収透過層とを備える。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

チューナブルバリアを備えるグラフェンスイッチング素子

【課題】チューナブルバリアを備えるグラフェンスイッチング素子を提供する。

【解決手段】バックゲート基板と、基板上のゲート絶縁層と、ゲート絶縁層上のグラフェン層と、グラフェン層の第1領域上に順次に積層された半導体層及び第1電極と、グラフェン層で第1領域と離隔している第2領域上の第2電極と、を備え、バックゲート基板とグラフェン層とは、半導体層を介して対向し、半導体層は、n型またはp型にドーピングされたチューナブルバリアを備えるグラフェンスイッチング素子。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能および製造安定性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、第1の面および第2の面を有する有機半導体部と、第1の面に隣接されたソース電極部と、第2の面に隣接されたドレイン電極部とを備える。ソース電極部およびドレイン電極部のうちの少なくとも一方は、有機半導体部よりも高導電性の有機半導体材料を含む高導電性電極部である。

(もっと読む)

集積されたダイオードを有するSOI基板を備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200は、ダイオード210及び絶縁層204を含むSOI基板(semiconductor on insulator)を備える。複合半導体装置200は、ダイオード210の上に形成された遷移体220及び遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

161 - 180 / 4,432

[ Back to top ]