Fターム[5F110HK34]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011)

Fターム[5F110HK34]の下位に属するFターム

Fターム[5F110HK34]に分類される特許

61 - 80 / 1,067

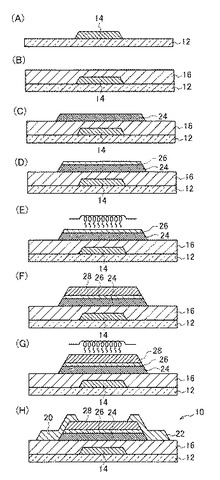

電界効果型トランジスタの製造方法、並びに、電界効果型トランジスタ、表示装置、イメージセンサ及びX線センサ

【課題】光照射時のTFT特性を安定化する。

【解決手段】ゲート電極14上に配置されたゲート絶縁層16上に、第一の酸化物半導体膜24を成膜する第一工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第二の酸化物半導体膜26を成膜する第二工程と、酸化性雰囲気の下300℃超で熱処理する第三工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第三の酸化物半導体膜28を成膜する第四工程と、酸化性雰囲気の下300℃超で熱処理する第五工程と、第三の酸化物半導体膜28上に、ソース電極20及びドレイン電極22を形成する電極形成工程と、を有している。

(もっと読む)

非晶質半導体膜の評価方法、及び半導体装置の製造方法

【課題】フラットパネルディスプレイの高性能化に伴い、その製造工程でのアモルファスシリコン(a−Si)膜の評価・管理の必要性が高まってきた。

【解決手段】ガラス基板上にa−Si膜を成膜した試料32に対してレーザ光照射手段36からレーザ光を照射する。試料32におけるレーザ光を照射した各サンプリング点に、マイクロ波照射手段38からマイクロ波を照射し、反射波検出手段40でその反射強度を測定する。各サンプリング点での反射強度の測定結果に基づいて、基板面内でのa−Si膜の物性の均一性を評価する。

(もっと読む)

半導体素子およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体素子およびその製造方法等を提供する。

【解決手段】半導体素子は、有機半導体層と、この有機半導体層と接するように配設された電極と、この電極とは別体として形成され、かつ電極と電気的に接続された配線層とを備えている。半導体素子の製造方法は、基板上に、有機半導体層およびこの有機半導体層と接する電極を形成する工程と、この電極と電気的に接続された配線層を形成する工程とを含んでいる。

(もっと読む)

半導体素子の製造方法及び電界効果型トランジスタの製造方法

【課題】光照射時の素子特性を安定化する。

【解決手段】酸化物半導体を主体とする半導体膜を成膜する第一工程と、第一工程後に、半導体膜の面上に第一の絶縁膜を成膜する第二工程と、第二工程後に、酸化性雰囲気中で熱処理する第三工程と、第三工程後に、第一の絶縁膜の面上に第二の絶縁膜を成膜する第四工程と、を有し、第二工程と前記第三工程の際に、第一の絶縁膜の厚みをZ(nm)とし、第三工程での熱処理温度をT(℃)とし、前記第一の絶縁膜及び前記半導体膜中への酸素の拡散距離をL(nm)としたとき、0<Z<L=8×10−6×T3−0.0092×T2+3.6×T−468±0.1の関係式を満たすように第一の絶縁膜の厚みと熱処理温度を調整する。

(もっと読む)

非晶質酸化物薄膜の製造方法及び薄膜トランジスタ

【課題】非晶質酸化物薄膜の膜質を向上する。

【解決手段】有機成分とInとを含有する第1酸化物前駆体膜4に対して有機成分の熱分解温度未満で有機成分の結合状態を選択的に変化させ、フーリエ変換型赤外分光で測定したときに得られる赤外線吸収スペクトルにおいて、赤外線の波数1380cm−1以上1520cm−1以下の範囲を赤外線の波数1380cm−1以上1450cm−1以下の範囲と赤外線の波数1450cm−1超1520cm−1以下の範囲とに分割したときに、赤外線の波数1380cm−1以上1450cm-1以下の範囲に位置するピークが、赤外線の波数1350cm−1以上1750cm−1以下の範囲における赤外線吸収スペクトルの中で最大値を示す第2酸化物前駆体膜6を得る前処理工程と、第2酸化物前駆体膜中に残存する有機成分を除去して、第2酸化物前駆体膜6を非晶質酸化物薄膜8へ変化させる後処理工程とを有する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が液晶性有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に液晶性有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】消費電力の増大を抑制し且つ微細化を達成した半導体装置および当該半導体装置の作製方法を提供する。また、安定した電気的特性が付与された、信頼性の高い半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜に電界で加速されたイオンを照射して、当該酸化物半導体膜の表面の平均面粗さを低減することにより、トランジスタのリーク電流の増大および消費電力の増大を抑制することができる。さらに、加熱処理を行って、酸化物半導体膜が当該酸化物半導体膜表面に垂直なc軸を有する結晶を含むように形成することにより、酸化物半導体膜の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】良好な特性を有する複数の有機トランジスタを備えた有機半導体素子の製造方法を提供する。

【解決手段】有機半導体素子10は、基板11と、基板11上に設けられ、各々が有機半導体材料を含む有機半導体領域4を有する複数の有機トランジスタ20と、を備えている。このうち有機半導体領域4は、少なくとも基板11を含む支持部材17によって支持されている。そして、有機半導体素子10の製造方法は、支持部材17を準備する工程と、支持部材17上に有機半導体材料を含む連続的な有機半導体層30を設ける工程と、有機半導体層30をパターニングして複数の有機半導体領域4を形成するパターニング工程と、を備えている。ここで、パターニング工程は、凹部42および凸部41を有する凹凸版40を準備する工程と、凹凸版40の凸部41を支持部材17上の有機半導体層30に当接させることにより有機半導体層30をパターニングする当接工程と、を有している。

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】バンク層の形成のために専用のマスクを用いたリソグラフィー工程が不要であり、製造工程を簡素化することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上にゲート電極12を形成した後、基体11及びゲート電極12上に絶縁層13を形成し、次いで、絶縁層13上に感光性絶縁材料から成るバンク層20を形成し、その後、基体側から、ゲート電極12を露光用マスクとして用いてバンク層20を露光し、ゲート電極12の上方のバンク層20を除去して、バンク層20に、ゲート電極の上方に位置する開口領域21を形成した後、塗布法に基づき、開口領域21内に半導体材料から成るチャネル形成領域14を形成し、その後、バンク層20上に一対のソース/ドレイン電極15を形成する各工程を備えている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

半導体装置及びその製造方法、並びに、画像表示装置の製造方法

【課題】本開示の目的は、ソース/ドレイン電極の段切れ、ソース/ドレイン電極の損傷といった問題の発生を確実に回避することができ、しかも、島状の平面形状を有するチャネル形成領域を確実に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基材11上にゲート電極12を形成した後、(b)基材11及びゲート電極12上に、チャネル形成領域14を形成すべき領域に凹部20が設けられたゲート絶縁層13を形成し、その後、(c)塗布法に基づき凹部20内に有機半導体材料から成るチャネル形成領域14を形成した後、(d)ゲート絶縁層13の上からチャネル形成領域14の一部の上に亙りソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

61 - 80 / 1,067

[ Back to top ]