Fターム[5F110HK34]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011)

Fターム[5F110HK34]の下位に属するFターム

Fターム[5F110HK34]に分類される特許

101 - 120 / 1,067

半導体装置

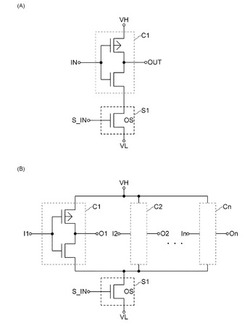

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチ

ングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングト

ランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチング

トランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気

的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半

導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体記憶装置

【課題】データ保持のためのリフレッシュ動作の頻度を低減し、消費電力の小さいDRAMを提供する。また、DRAMに占めるキャパシタの面積を縮小し、集積度の高い半導体記憶装置を提供する。

【解決手段】ビット線、ワード線、トランジスタおよびキャパシタからなる半導体記憶装置であり、トランジスタは、ソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極の上面と接する酸化物半導体膜と、少なくとも酸化物半導体膜の上面と接するゲート絶縁膜とを有し、上面から見て網状の導電膜の網の目の部分に設けられる。ここで、キャパシタは、一対の電極の一方と、網状の導電膜と、一対の電極の一方および網状の導電膜の間に設けられた第2の絶縁膜と、を有する。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】本発明は、有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供することを主目的とする。

【解決手段】本発明は、ソース電極およびドレイン電極を覆うように、低分子有機半導体材料を有する有機半導体層を形成する有機半導体層形成工程と、上記ソース電極および上記ドレイン電極間のチャネル領域を含むように、上記有機半導体層上に第一誘電体層を形成する第一誘電体層形成工程と、上記低分子有機半導体材料を溶解することができる溶媒で、上記有機半導体層の一部を洗浄することにより、第一誘電体層非形成領域の上記有機半導体層を除去する洗浄除去工程と、上記第一誘電体層を覆うように第二誘電体層を形成する第二誘電体層形成工程と、を有することを特徴とする有機半導体素子の製造方法を提供することにより、上記課題を解決する。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供す

ることを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導

体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードであ

る。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれ

る電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度

化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導

体よりもバンドギャップが大きい。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ液晶表示装置の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極、ゲート絶縁層、活性層及びソースドレイン電極を有した薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソースドレイン電極と該活性層のソースドレイン領域は重なり、該活性層と前記ソースドレイン電極間に電子の走行を許容する薄いSiNx又はSiOxNy層が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗が小さく高性能なナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1方向に延在するナノワイヤ形状のチャネル領域3と、チャネル領域3を間に挟むように離間して設けられかつチャネル領域3よりも幅が広いソース領域およびドレイン領域8,9と、チャネル領域3、ソース領域およびドレイン領域8,9と基板との間に設けられ膜厚が薄い凹形状の領域を有する絶縁膜2と、チャネル領域3上の半導体層の少なくとも側面に設けられたゲート絶縁膜と、前記ゲート絶縁膜に対して前記第1領域上の前記半導体層と反対側に設けられたゲート電極6と、ゲート電極6の、ソース領域およびドレイン領域8,9に対向する側面に設けられた絶縁体のゲート側壁7と、を備え、半導体層は半導体層直下の前記凹形状の領域の部分に延在している。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

表示装置の作製方法

【課題】表示装置の作製工程で紫外線の照射を行っても、酸化物半導体層を用いた薄膜ト

ランジスタのしきい値電圧のシフトを低減させることができる、表示装置の作製方法を提

供することを課題の一つとする。

【解決手段】少なくとも一回以上の紫外線の照射を行い、且つ酸化物半導体層を有する薄

膜トランジスタをスイッチング素子として用いる、表示装置の作製方法において、全ての

紫外線照射工程を終えた後で、紫外線照射による該酸化物半導体層のダメージを回復させ

る熱処理を行う表示装置の作製方法である。

(もっと読む)

半導体装置

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供すること

を目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物

半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで

、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注

入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び

、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

薄膜素子組立体

【課題】巻き取りを行っても傷や損傷が発生し難い構成、構造を有する薄膜素子組立体を提供する。

【解決手段】薄膜素子組立体にあっては、可撓性を有する基材20の第1面21上に複数の薄膜素子10が備えられており、基材20において、複数の薄膜素子10が備えられた第1領域の外側に、薄膜素子を備えていない第2領域が設けられており、基材20の第1面21の第2領域、又は、第2面22の第2領域、又は、第1面21及び第2面22の第2領域に凸部31が形成されている。

(もっと読む)

半導体装置の作製方法及びプラズマ酸化処理方法

【課題】窒素を含むゲート絶縁膜にプラズマ酸化処理を行うことで、薄膜トランジスタの特性の低下を抑制できる半導体装置の作製方法を提供する。

【解決手段】本発明の一態様は、ゲート電極103、窒素を含むゲート絶縁膜105、微結晶半導体膜107,109によって形成されたチャネル領域を有する薄膜トランジスタを備えた半導体装置の作製方法であって、前記ゲート絶縁膜を、酸素原子を含む酸化ガスと水素とを有する酸化ガス雰囲気のプラズマに曝すプラズマ処理を行い、前記ゲート絶縁膜上に前記微結晶半導体膜を形成し、前記酸化ガス雰囲気における前記水素の量をaとし、前記酸化ガスの量をbとした場合に下記式(1)、(2)を満たすことを特徴とする半導体装置の作製方法。

a/b≧2 ・・・(1)

b>0 ・・・(2)

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

101 - 120 / 1,067

[ Back to top ]