Fターム[5F110QQ16]の内容

Fターム[5F110QQ16]の下位に属するFターム

素子形成前に貼り合わせ (694)

Fターム[5F110QQ16]に分類される特許

101 - 120 / 611

結晶化半導体薄膜の製造方法および結晶化半導体薄膜

【課題】アモルファス薄膜の溶融結晶化時に生じる凹凸の影響を受けないようなトップゲート型TFT素子などの作製が可能な結晶化半導体薄膜の製造方法および該凹凸が表面にない結晶化半導体薄膜を提供する。

【解決手段】本発明の結晶化半導体薄膜の製造方法は、第1基板1上層に剥離層2を介して剥離可能に形成したアモルファス半導体薄膜4aを溶融結晶化させ、その後、結晶化した結晶化半導体薄膜4pの表面側を接合面にして接着剤6を介して第2基板5上層に前記結晶化半導体薄膜4pを接合するとともに該結晶化半導体薄膜4pを第1基板側1から剥離する。本発明の結晶化半導体薄膜は、基板上層に設けられた結晶化半導体薄膜であって、該結晶化半導体薄膜は、前記基板上層に接合層を介して接合されており、かつ該接合層に対する接合面側に溶融結晶化に伴う凹凸形状を有する。

(もっと読む)

半導体表示装置

【課題】プロセスを複雑化することなく、高速動作を確保し、なおかつ高い耐圧性も確保することができる駆動回路を用いた半導体表示装置の提供を、目的の一とする。或いは、プロセスを複雑化することなく、消費電力を抑え、なおかつ高い耐圧性も確保することができる駆動回路を用いた半導体表示装置の提供を、目的の一とする。

【解決手段】シリコンまたはゲルマニウムよりもバンドギャップが大きく、真性キャリア密度が低い半導体で、耐圧性の高さが要求される回路を作製する。このような半導体としては、例えば、シリコンの約3倍程度の大きなバンドギャップを有する、酸化物半導体が挙げられる。さらに、シリコンまたはゲルマニウムなどを有する結晶性半導体で、耐圧性の高さがさほど要求されない回路を作製する。そして、上記2つの回路を接続することで、半導体表示装置を作製する。

(もっと読む)

画像表示装置及びその製造方法

【課題】多面取りで製造される画像表示装置の切断面からの水分や酸素等のTFT層への侵入を防止することが可能な画像表示装置及びその製造方法を提供することである。

【解決手段】

湾曲可能な透明基板からなる第1基板と、前記第1基板に接着され、その上層に薄膜トランジスタが形成される樹脂フィルム層とを備える画像表示装置であって、前記樹脂フィルムの表面を被う無機膜からなるバリア層を備え、前記バリア層を介して、前記樹脂フィルムの上層及び下層に薄膜層が形成される画像表示装置である。

(もっと読む)

半導体基板を製造する方法

【課題】 半導体基板、特に半導体・オン・インシュレータ基板を製造する新規な方法を提供する。

【解決手段】 本発明の半導体基板を製造する方法は、a)ドナー基板とハンドル基板を準備するステップと、b)ハンドル基板に、特に内部に、1つ以上のドープ領域のパターンを形成するステップと、c)次に、特に結合させることにより、ドナーとハンドル基板を付着させて、ドナー・ハンドル複合物を得るステップと、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】高さの異なる複数の素子形成面に形成された半導体素子の電気特性を均一化する。

【解決手段】半導体装置Sは、高さの異なる複数の素子形成面50が段差状に形成された半導体層1と、素子形成面50を含む各領域にそれぞれ形成された半導体素子51,52と、半導体層1に対し、半導体素子51,52を覆うと共に素子形成面50に沿った段差状の表面を有する段差補償絶縁膜28とを備えている。そして、各素子形成面50における半導体層1は、互いに同じ厚みに形成されている。

(もっと読む)

電気光学装置用基板の製造方法、電気光学装置用基板、電気光学装置及び電子機器

【課題】例えば電極パッドと薄膜素子との間に剥離層を介して静電結合が生じることを低減する。

【解決手段】電気光学装置用基板の製造方法は、転写元基板(10)に形成した薄膜素子(310)を転写先基板(70)に転写することにより電気光学装置用基板を製造する製造方法であって、転写元基板上に設けられた剥離層(11)上に絶縁膜(5)を介して薄膜素子を形成する工程と、転写元基板上における薄膜素子よりも上層側に電極パッド(500)を形成する工程と、転写元基板上の積層構造における絶縁膜と電極パッドとの間に、転写元基板上で平面的に見て電極パッドに少なくとも部分的に重なるように、遮蔽電極(710)を形成する工程とを含む。

(もっと読む)

半導体装置の作製方法

【課題】剥離工程を簡略化し、且つ大型基板に対する剥離・転写を均一に行う半導体装置

の方法を提供する。

【解決手段】第1の基板上に金属膜を形成し、金属膜に接して珪素を有する絶縁膜を形成

すると金属膜の表面には酸化金属膜が形成されている。そして、絶縁膜上に薄膜トランジ

スタ等の半導体素子を形成する。第1の接着剤を用いて、半導体素子上に第2の基板を固

定し、かつ第1の基板を分離し、第2の接着剤を用いて、半導体素子下にフィルム基板等

の第3の基板を固定し、かつ第2の基板を分離するときに、紫外線を照射することによっ

て、第1の接着剤の粘着性の低下又は剥離と、第2の接着剤の硬化とを同時に行う。

(もっと読む)

半導体装置及びその作製方法

【課題】プラスチックフィルム基板などの柔軟性を有するフレキシブル基板に転写後のデバイスに対してFPCを圧着する際、クラック等の不良発生を防止する。

【解決手段】転写する被剥離層として、素子を有する回路を含む層405aと、端子電極405bとを形成し、その上にクラックを防止するための樹脂からなる保護層405cを形成す。FPCの接続を行う部分において、端子電極の電極面が露出している。FPC407を圧着して異方性導電フィルム406により接続を行う。この圧着工程において、保護層405cによって配線が保護されているため、加圧変形によるクラックの発生を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】転写元基板上に形成された被転写層を転写先基板に転写して半導体装置を製造する際に、転写元基板を容易に剥離できる半導体装置の製造方法を提供すること。

【解決手段】転写元基板1の表面に剥離層2を形成する工程と、前記剥離層2上に被転写層5を形成する工程と、前記転写元基板1の裏面に引っ張り応力を有する剥離助長層6を形成する工程と、前記被転写層5上に転写先基板8を接着する工程と、前記剥離層2に光または熱を照射して前記被転写層5を剥離する工程と、を含むことを特徴とする。

(もっと読む)

グラフェン・ベースの三次元集積回路デバイス

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを有する半導体装置において、より高い耐衝撃性を付与することを目的の一とする。より多様化する用途に対応でき、利便性が向上した信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】半導体装置において、基板上に、ゲート電極層と、ゲート絶縁層と、酸化物半導体層とを含むボトムゲート構造のトランジスタと、トランジスタ上に絶縁層と、絶縁層上に導電層とを有し、絶縁層は酸化物半導体層を覆い、かつゲート絶縁層と接して設けられ、酸化物半導体層のチャネル幅方向において、ゲート電極層上でゲート絶縁層と絶縁層とは端部が一致し、導電層は、酸化物半導体層のチャネル形成領域と、ゲート絶縁層及び絶縁層の端部とを覆い、かつゲート電極層と接して設けられる。

(もっと読む)

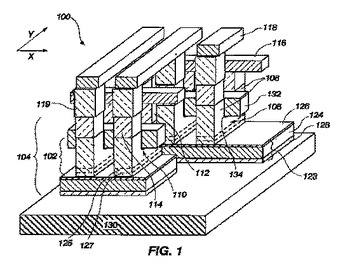

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】3次元デバイスのような多層配線を有する半導体装置をより簡単な工程で作製する製造方法を提供する。

【解決手段】第1層10と第2層20とを、それぞれのTSV6が略一直線上になるように積層する半導体装置の製造方法で、基板の上面に入出力回路を構成するトランジスタ3を形成し、トランジスタ3を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第1層の製造工程と、基板20を準備し、基板の上面に論理回路を構成するトランジスタ13を形成し、トランジスタ13を覆うように絶縁層4を形成し、絶縁層中にTSV6を形成する工程を含む第2層の製造工程と、第1層のTSV6と第2層のTSV6とが略一直線上になるように、第1層と第2層の、基板の反対側面を接続する接続工程と、第1層の基板1を除去する工程とを含む。

(もっと読む)

薄膜素子群の転写方法

【課題】本発明の目的の一つは、薄膜素子群110を製造元基板100から転写先基板200に転写する際に、製造元基板100が割れて仕舞う事を防止する事が出来る、薄膜素子群の転写方法を提供する事にある。

【解決手段】本発明の一態様としての薄膜素子群の転写方法は、薄膜素子群110が形成された製造元基板100の周辺部、及び転写先基板200の周辺部の少なくとも一方に凹凸部790を有する撥水領域130を生成する表面処理工程と、製造元基板100の製造元基板表面及び転写先基板200の製造元基板表面の少なくとも一方に水溶性接着剤160を塗布する接着剤塗布工程と、製造元基板100の製造元基板表面と転写先基板200の転写先基板とを対向させて貼り合わせる基板配置工程と、水溶性接着剤160を硬化させる接着剤硬化工程と、製造元基板100を転写先基板200から剥離させる事に依って、薄膜素子群110を転写先基板200に転写する基板剥離工程と、を有する事を特徴とする。

(もっと読む)

半導体装置

【課題】様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】強磁性材料からなるシートを支持体とし、前記強磁性材料からなるシートに接する接着材と、該接着材に接する絶縁膜上に素子とを備える。上記構成において、前記素子は、薄膜トランジスタ、有機化合物を含む層を有する発光素子、液晶を有する素子、メモリー素子、薄膜ダイオード、シリコンのPIN接合からなる光電変換素子、またはシリコン抵抗素子であってもよい。また、上記各構成において、前記強磁性材料からなるシートは、軟質磁性粉体と合成樹脂とを混合して形成され、着磁されたものであってもよい。

(もっと読む)

発光装置及び電子機器

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥

離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを

可能とすることを目的する。また、様々な基材に被剥離層を貼りつけ、軽量された半導体

装置およびその作製方法を提供することを課題とする。

【解決手段】基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を

設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化

を行い、金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または

金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の駆動能力の向上を図ることを課題の一とする。

【解決手段】半導体装置は、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタの第1の端子は、第1の配線と電気的に接続され、第1のトランジスタの第2の端子は、第2の配線と電気的に接続され、第2のトランジスタのゲートは、第3の配線と電気的に接続され、第2のトランジスタの第1の端子は、第3の配線と電気的に接続され、第2のトランジスタの第2の端子は、第1のトランジスタのゲートと電気的に接続され、第1のトランジスタ及び第2のトランジスタは、酸化物半導体によりチャネル領域が形成され、第1のトランジスタ及び第2のトランジスタのチャネル幅が1μmあたりのオフ電流が1aA以下である。

(もっと読む)

紫外線センサを有する半導体装置及びその作製方法

【課題】安価に製造することができ、フレキシブルな基板上に形成することが可能な高精度な紫外線センサを提供することを課題とする。

【解決手段】酸化物半導体膜を有するトランジスタと、前記トランジスタのゲートに接続する電圧源を有し、前記トランジスタのしきい値電圧は前記酸化物半導体膜に紫外線を照射することによって変化し、前記トランジスタのしきい値電圧の変化は酸化物半導体膜に照射される紫外線の波長に依存し、前記電圧源は前記トランジスタのゲートに出力する電圧を調整する構成を有する半導体装置。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的する。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

【解決手段】基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い、金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

101 - 120 / 611

[ Back to top ]