Fターム[5F140AA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 相互コンダクタンスの向上 (502)

Fターム[5F140AA05]に分類される特許

141 - 160 / 502

半導体装置の製造方法および半導体装置

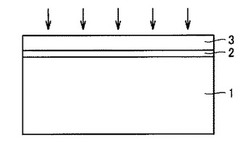

【課題】SiO2/SiC構造を備える、たとえばMOSFETなどの半導体装置は、界面準位密度の低減が不十分である。

【解決手段】SiC基板1の一方の主表面上に形成させたSiCエピタキシャル層2の一方の主表面上に、あらかじめSi薄膜3を形成させて、このSi薄膜3の内部に窒素原子を注入させる。この状態で、SiCエピタキシャル層2の一方の主表面上を酸窒化させる。

(もっと読む)

半導体デバイス

【課題】特徴サイズの小さいMOSトランジスタとその製造方法を提供する。

【解決手段】本発明は、ショートチャネルの影響を低減し、薄くドープしたドレイン領域(LDD構造)を有さない。MOSトランジスタのゲート長さは1.25μm以下である。本発明のMOSトランジスタはゲート酸化物層を含み、この層は基板との間で平面状でかつストレスのないインタフェースを形成する。その結果、ホットキャリアの発生およびホットキャリアの悪影響が回避できる。LDD構造を省略したために、製造プロセスの複雑さが低下し、ソース−ドレインの直列抵抗が減り、その結果駆動電流と切り換え速度が改善された。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

半導体装置およびその製造方法、並びにMOS型電界効果トランジスタおよびその製造方法

【課題】III族窒化物系化合物半導体の表面上に酸化物を備えた半導体装置であって、上記III族窒化物系化合物半導体と上記酸化物との間の界面の界面準位密度を小さくでき、移動度を高くできるものを提供すること。

【解決手段】本発明の半導体装置では、III族窒化物系化合物半導体3の表面上に、Alを組成に含みスピネル構造をもつ酸化物4が形成されている。III族窒化物系化合物半導体3は、例えばGaNからなる。酸化物4は、例えばMgAl2O4、MnAl2O4、CoAl2O4、NiAl2O4からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置

【課題】半導体装置の電流駆動能力の向上および電流駆動能力の変動の抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板200と、半導体基板200の主表面に形成された溝部内に埋め込まれた素子分離絶縁膜104と、半導体基板200の主表面上に形成されたゲート電極120と、ゲート電極120と隣り合う部分に形成されたソース領域111と、ゲート電極120と隔てて設けられたゲート電極150と、ゲート電極150と隣り合う部分に形成されたソース領域141と、ソース領域111,141を覆うように形成され、素子分離絶縁膜104が半導体基板200に加える応力と反対方向の応力を半導体基板に加えるストレス絶縁膜130を備え、ゲート電極120の隣りに位置する部分は、ゲート電極120下に位置する部分よりも下方に位置し、ゲート電極150の隣りに位置する部分からゲート電極150下に達する部分は、実質的に面一とされる。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度の向上を実現し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたチャネル領域44上にゲート絶縁膜18を介して形成されたゲート電極20bと、ゲート電極の側壁部分に形成されたサイドウォール絶縁膜26と、ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層38と、ソース/ドレイン拡散層に埋め込まれ、半導体基板と格子定数が異なる半導体層52とを有し、半導体層は、半導体基板のうちのサイドウォール絶縁膜の下方領域に食い込むように形成された第1の突出部54と、半導体基板のうちのサイドウォール絶縁膜の直下の部分に食い込むように形成された第2の突出部56とを有している。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】炭化珪素半導体装置の、半導体基板と酸化膜との界面近傍における界面準位密度を低減して、チャネル移動度を向上させることのできる炭化珪素半導体装置とその製造方法とを提供すること。

【解決手段】炭化珪素の半導体基板1の表面にシリコン酸化膜を主成分とする酸化物層を形成する工程を含む炭化珪素半導体装置の製造方法において、酸化物層の、炭化珪素エピタキシャル層2と対向しない一方の主表面をIII族元素を含有するガスに加熱雰囲気中で曝露して、酸化物層にIII族原子を含有させる。そして、酸化物層と半導体基板1との界面近傍に拡散させたIII族原子により界面準位を終端させ、炭化珪素半導体装置のチャネル移動度を向上させる。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に対し応力歪みを与えるトランジスタを形成する際に、他の導電型領域で生じるカバー膜のエッチング量を低減することが可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、はじめに、上面上にゲート絶縁膜2、ゲート電極3およびサイドウォール5が形成された半導体基板1を準備する。次に、半導体基板1上にカバー膜7を形成し、第1導電型のトランジスタ形成領域のカバー膜7上にフォトレジスト膜8を形成する。次に、第2導電型のトランジスタ形成領域のカバー膜7をエッチング除去し、さらに同じエッチング装置で第2導電型のトランジスタ形成領域に第1の溝10を形成する。次に、フォトレジスト膜8を除去し、等方性エッチングを行い第2の溝11を形成する。最後に、第2の溝11に半導体基板1と格子定数の異なる半導体材料を埋め込み、ソース・ドレイン領域6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造工程におけるストレス印加およびアニールによる転位、結晶欠陥を抑え、チャネル領域において良好なストレスを印加するとともに、低抵抗化と浅接合化の両立を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法において、半導体基板表面に前記半導体基板表面の面積に対する開口率が5〜30%の開口部を形成する工程と、前記開口部内に15〜25%の範囲の濃度で前記半導体基板を構成する原子と異なる格子定数を有する第2の原子を含む混晶からなるエピタキシャル層を形成する工程と、前記エピタキシャル層にイオン注入する工程と、所定の温度Tで活性化アニールを行う工程とを備え、前記所定の温度Tは、1150℃以上かつT≦1E−5exp(21541/T)からなる関係を満たす。

(もっと読む)

半導体装置

【課題】MISトランジスタにおいて、リーク電流の発生を抑え、チャネル移動度と信頼性とを共に向上させた半導体装置を提供する。

【解決手段】半導体装置は、第1のウエル領域3a及び第2のウエル領域3bと、素子分離領域2に囲まれた第1の活性領域21aと、素子分離領域2、2Bに囲まれた第2の活性領域21bと、第1の活性領域21a上に形成され、凹部内に埋め込まれたSi混晶層からなるソース/ドレイン領域を有する第2導電型の第1のMISトランジスタMP2と、第2の活性領域21b上に形成された第1導電型の第2のMISトランジスタMN2と、第1の活性領域21a上に形成された第2導電型の分離用MISトランジスタDP2とを備える。第1のMISトランジスタのソース/ドレイン領域は、第1の活性領域21aにおけるゲート長方向の端部に位置する素子分離領域2に接していない。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、MOSFETのチャネル領域に生じる歪み量を増加させ、歪みに基づく素子性能を向上させることを目的とする。

【解決手段】 本発明に係る半導体装置は、半導体基板1と、半導体基板1の上面に、第1の方向に延びて設けられた第1の絶縁膜2aと、第1の方向と垂直な第2の方向から第1の絶縁膜2aを挟んで設けられ、第1の絶縁膜2aに第2の方向の応力を与え、第1の方向の歪みを誘起させる第1の歪み誘起層3と、第1の絶縁膜2a上に設けられ、第1の絶縁膜2aからの応力を受けて第1の方向の歪みを有するチャネル領域4を含む第1の半導体層5aと、第1の方向からチャネル領域を挟んで設けられたソース領域9及びドレイン領域10と、第1の半導体層5aの第2の方向に対向する側面及び上面に設けられたゲート絶縁膜6と、ゲート絶縁膜6を介してチャネル領域4と対向して設けられたゲート電極7とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化された構造においても効果を発揮する歪みシリコン技術を適用した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板中の前記ゲート絶縁膜下に形成されたチャネル領域と、前記チャネル領域の両側に形成された第1の層、および前記第1の層の下層に位置し、ゲート電極中央側の端部の位置が前記第1の層よりも前記ゲート電極中央に近い第2の層を含み、前記チャネル領域に歪みを発生させる歪み付与層と、前記チャネル領域の両側に、少なくとも一部が前記歪み付与層と重なるように形成されたソース・ドレイン領域と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】Nチャネル絶縁ゲート型電界効果トランジスタのシリコンのチャネル領域に引張応力を効果的に印加することを可能とし、また寄生トランジスタの移動度を高めることを可能にする。

【解決手段】シリコン基板11と、前記シリコン基板11に区画された素子形成部12と、前記素子形成部12に形成されたNチャネル絶縁ゲート型電界効果トランジスタ20と、前記シリコン基板11に形成されていて前記素子形成部12の側部を囲む溝部13と、前記溝部13内に絶縁材料が埋め込まれて形成された素子分離部14と、少なくとも前記Nチャネル絶縁ゲート型電界効果トランジスタ20のチャネル長L方向と平行な前記溝部13の側面に形成されたシリコンゲルマニウムエピタキシャル成長層15を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】STIの圧縮応力を減少し、チャネル方向とチャネル幅方向の応力を印加することにより、駆動能力を増大したCMOS半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

(もっと読む)

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MISFETの移動度劣化を抑制する。

【解決手段】nMISFETQnは、基板1上にゲート絶縁膜3を介してゲート電極4を有している。ゲート絶縁膜3は、酸化シリコンよりも誘電率が高く、ハフニウムを含む酸化膜を有している。ゲート電極4は、ゲート絶縁膜3上に窒化チタン膜5と、窒化チタン膜5上にニッケルリッチのフルシリサイド膜6とを有している。pMISFETQpは、基板1上にゲート絶縁膜11を介してゲート電極12を有している。ゲート絶縁膜11は、酸化シリコンよりも誘電率が高く、ハフニウムを含む酸化膜を有している。ゲート電極12は、ゲート絶縁膜11上にニッケルリッチのフルシリサイド膜6を有している。

(もっと読む)

141 - 160 / 502

[ Back to top ]