Fターム[5F140AA23]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | ホットキャリア、ホットエレクトロン効果対策 (101)

Fターム[5F140AA23]に分類される特許

1 - 20 / 101

半導体装置の製造方法

半導体装置およびその製造方法

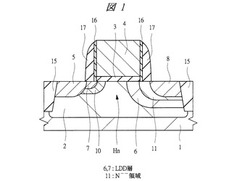

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

(もっと読む)

半導体装置及びその駆動方法

【課題】閾値電圧(Vth)の経時的に変動する現象を抑制することで、高信頼性を保つことが可能なMIS型半導体装置を提供する。

【解決手段】本発明は、半導体ボディ領域とゲート絶縁膜の間に半導体ボディ領域とは逆の半導体極性のチャネル層を有するMIS型半導体装置であり、当該半導体装置のフラットバンド電圧Vfbを−10ボルト以下とすることにより、半導体ボディ領域表面近傍に誘起されるキャリア電荷密度を当該半導体装置の動作保証範囲内において所定量以下に抑制する。

(もっと読む)

半導体デバイスのための非対称スペーサ構造体を形成する方法

【課題】 デバイスのゲートとソースとの間の低い直列抵抗を維持し、同時に、ゲートからドレインへの過剰なオーバーラップによって形成される悪影響を最小限にするFETデバイスの製造を可能にする。

【解決手段】半導体基板の上に少なくとも1対の隣接して離間配置された、オフセット・スペーサ114を備えるゲート構造体102の上にスペーサ層132を形成するステップであって、ゲート構造体は、スペーサ層がゲート構造体間の領域で第1の厚さで形成され、その他の場所で第2の厚さで形成されるように離間配置され、第2の厚さは第1の厚さより厚い、ステップと、1対の隣接して離間配置されたゲート構造体のオフセット・スペーサに隣接して非対称スペーサ構造体124a、bを形成するようにスペーサ層をエッチングするステップとを含み、非対称スペーサ構造体は、ソース及びドレイン領域の画定において用いられる。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】MISFETにおいて、信頼性寿命の低下を抑制する。

【解決手段】半導体装置100は、少なくとも1つのMISFETを備える。MISFETは、第1導電型の半導体基板101と、半導体基板101上にゲート絶縁膜104を介して形成されたゲート電極105と、半導体基板101におけるゲート電極105の側方に形成された第2導電型のソース領域106と、他方の側方に形成された第2導電型のドレイン領域107と、半導体基板101におけるゲート電極105の下方であり且つソース領域106及びドレイン領域107に挟まれたチャネル領域111とを備える。ゲート絶縁膜104は、ゲート電極105の底面下から側面上にまで亘って形成されている。チャネル領域111において、ドレイン領域107近傍の第1領域における不純物濃度は、チャネル領域111における第1領域以外の第2領域における不純物濃度に比べて低い。

(もっと読む)

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタにおいて、ホットエレクトロンのゲート絶縁膜へのトラップによるトランジスタ特性の経時劣化を減少させる。

【解決手段】N−−型の半導体層12の表面にボディ層19が配置されている。ボディ層19の表面にはN−型層23を含むソース層が配置されている。N−−型の半導体層12の表面には、N−型のドリフト層21が形成されている。このドリフト層21は、N型不純物濃度のピーク領域P1を有した第1の領域21Aと、この第1の領域21Aに隣接し、N型不純物濃度のピーク領域P1よりも深い位置にN型不純物濃度のピーク領域P2を有した第2の領域21Bとにより構成されている。第2の領域21Bの表面にはN+型のドレイン層25が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、ゲート絶縁膜の一方の側のみに、容易に、かつ精度良く、バーズビークを形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】斜めイオン注入により、マスク膜にイオンを注入することで、シリコン酸化膜及びシリコン窒化膜を介して、ゲート絶縁膜の第1の側面と第1の不純物拡散領域の上面とで構成される角部に形成されたマスク膜のエッチング速度を、他の部分に形成されたマスク膜よりも速くし、次いで、ウエットエッチングにより、角部に形成されたマスク膜を選択的に除去して、シリコン窒化膜の表面の一部を露出させ、次いで、ウエットエッチングにより、マスク膜から露出されたシリコン窒化膜を選択的に除去して、シリコン酸化膜の表面の一部を露出させ、その後、熱酸化法により、ゲート絶縁膜の第1の側面側にバーズビークを形成する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセスばらつきの影響が小さい半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板の上層部分に設けられた第1導電形領域と、前記第1導電形領域の上層部分に相互に離隔して配置された第2導電形のソース領域及びドレイン領域と、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、を備える。そして、前記第1導電形領域のうち前記ゲート電極の直下域に相当するチャネル領域における実効的な不純物濃度は、前記ゲート絶縁膜との界面において最も高く、下方に向かうにつれて減少している。

(もっと読む)

半導体装置

【課題】 半導体装置の耐圧性を向上させることを目的とする。

【解決手段】 半導体基板10と、半導体基板10上に形成されたゲート絶縁膜11と

、を備え、半導体基板10が、ゲート絶縁膜直下領域13に対して、ゲート絶縁膜直下領

域13のドレイン領域側側部領域14が掘り込まれた構造を有する。さらに、半導体基板

10が、ゲート絶縁膜直下領域13に対して、ゲート絶縁膜直下領域13のソース領域側

側部領域15が掘り込まれた構造を有する。

(もっと読む)

回路シミュレータおよび半導体装置の設計方法

【課題】インパクトイオン化電流の算出精度を向上させる。

【解決手段】飽和ソース−ドレイン電圧Vdsatがソース−ゲート電圧Vgsおよびソース−ドレイン電圧Vdsの関数にて与えられたドレイン横方向電界Edの計算式に基づいて電界効果トランジスタのインパクトイオン化電流Iiiを計算する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の端部にトラップされるホットキャリアの数を抑制し、且つ、面積拡大を抑制しつつ高耐圧のMOSトランジスタを作製する。

【解決手段】第1導電型の半導体基板1上に形成したマスクパターン9をマスクとして、第2導電型の一対の第1低濃度拡散領域4と、第1低濃度拡散領域4よりも深くかつ高濃度の第2導電型の一対の第2低濃度拡散領域3と、を形成する。そして、一対の第1低濃度拡散領域4のうちの一方の第1低濃度拡散領域4上から他方の第1低濃度拡散領域4上に亘ってゲート絶縁膜5を形成し、このゲート絶縁膜5上にゲート電極6を形成する。そして、ゲート電極6をマスクとして、第2低濃度拡散領域3よりも高濃度の第2導電型の一対の高濃度拡散領域8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

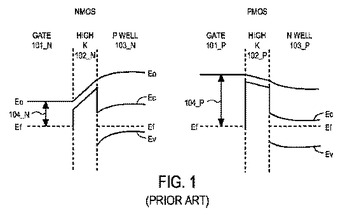

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

MOS型半導体装置

【課題】所望の位置に所望の厚さのゲート酸化膜を有する、高性能かつ長寿命のMOS型半導体を提供すること。

【解決手段】半導体基板と、該半導体基板上にゲート酸化膜を介して形成されたゲート電極とを含み、該ゲート酸化膜の両端部に接するように該半導体基板上にそれぞれ設けられた、該半導体基板の導電型とは異なる導電型の不純物を含む2つの不純物活性領域をそれぞれソース電極及びドレイン電極とする、MOS型半導体装置であって、該ゲート酸化膜を介して形成されたゲート電極は、それぞれが該半導体基板とゲート酸化膜を介して形成された構造を有する複数の領域からなり、各領域の該ゲート酸化膜の厚さが少なくとも2種類の異なる厚さで構成され、該各領域は互いに接合されている、ことを特徴とするMOS型半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

1 - 20 / 101

[ Back to top ]