Fターム[5F140BA02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiC (638)

Fターム[5F140BA02]に分類される特許

201 - 220 / 638

半導体装置の製造方法

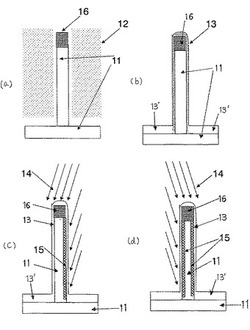

【課題】 これまでのイオン注入処理に比べて、高い時間効率で高濃度のキャリア不純物原子を、通常のイオン注入の処理時間で低エネルギードーピングできる方法を提供する。

【解決手段】 半導体基板としてのシリコン基板11の表面上に加工により突出部を形成した該シリコン基板の内部においてドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜13としてシリコン基板の表面上に堆積する工程と、前記突出部における前記堆積膜の斜め上方からイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記突出部の表面内部にリコイルさせる工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

制御されたアニールによる炭化シリコンパワーデバイスの製造方法

【課題】深いp型注入領域から浅いn型注入領域を囲む炭化シリコンの表面への好ましい拡散が可能な高性能炭化シリコン・パワーデバイスを製造する。

【解決手段】炭化シリコン基板の表面に開口部を確定し、その開口部を通して炭化シリコン基板内にp型ドーパントを深いp型注入領域を形成する注入エネルギー及び注入量で注入し、その開口部を通して炭化シリコン基板内にn型ドーパントを深いp型注入領域と比較して浅いn型注入領域を形成する注入エネルギー及び注入量で注入する。深いp型注入領域を横方向へ浅いn型注入領域を囲む炭化シリコン基板の表面まで拡散させるのに十分で、深いp型注入領域を縦方向に浅いn型注入領域を通って、炭化シリコン基板の表面まで拡散させることがないように、深いp型ドーパントと浅いn型ドーパントを1650℃未満だが好ましくは約1500℃よりも高い温度で約5分から約30分の間だけアニールする。

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

イオン注入及び側方拡散による炭化シリコンパワーデバイスの自己整列的な製造方法

【課題】自己整列した浅い注入領域及び深い注入領域を形成し、浅い注入領域の低い拡散率を有するn型ドーパントを比較的固定すると共に、深い注入領域の高い拡散率を有するp型ドーパントを十分に拡散させ、良く制御されたチャネルを形成するpベース領域をn型ソースの周りに形成して横型炭化シリコンパワーデバイスを製造する。

【解決手段】炭化シリコン基板内にマスクの開口部を通してp型ドーパントをイオン注入して深いp型注入領域を形成する。マスクの同じ開口部を通してn型ドーパントをイオン注入して前記p型注入領域と比較して浅いn型注入領域を形成する。その後、前記深いp型注入領域を前記浅いn型注入領域を囲む炭化シリコン表面まで、該埋め込まれた深いp型注入領域を該浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間でアニールする。

(もっと読む)

バルクFinFET中のSiフィンのフィン下部近くのSTI形状

【課題】半導体フィンとフィン型電界効果トランジスタの構造、及び、製造方法を提供する。

【解決手段】集積回路構造の形成方法は、頂面を有する半導体基板を提供するステップと、半導体基板中に、第1絶縁領域と第2絶縁領域を形成するステップと、第1絶縁領域と第2絶縁領域を陥凹するステップと、からなる。第1絶縁領域と第2絶縁領域の残り部分の頂面は平らな表面であるか、或いは、窪み表面である。第1絶縁領域と第2絶縁領域の除去部分間の半導体基板の部分、及び、隣接する部分は、フィンを形成する。

(もっと読む)

シリコン選択エッチ方法

基板上に設けられるシリコン層をエッチングする方法は、シリコン層に第1のトレンチを異方性エッチングすること;第1のトレンチ内のシリコン表面を選択的に異方性ウェットエッチングすることであって、該ウェットエッチングが、シリコン表面を、芳香族トリ(低級)アルキル第四級オニウム水酸化物と、非対称テトラアルキル第四級ホスホニウム塩とを含む水性組成物に曝すことを含み、該ウェットエッチングが、シリコン層の(110)面及び(100)面をおよそ等しい速度で(111)面よりも優先的にエッチングして、(111)面に側壁を有する拡大されたトレンチを形成する、選択的に異方性ウェットエッチングすることを含む。応力をシリコン層の少なくとも一部分に導入するプロセスの一環として、このようにして作製したトレンチ内にシリコン合金をエピタキシャル堆積させてもよい。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】SiCを酸化する際に生成された炭素が不純物として酸化膜(SiO2)中に残留してしまうことを抑制し、チャネル移動度を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、炭化シリコンを含む基板11上に酸化シリコン膜12を形成する工程と、酸化シリコン膜12上に金属酸化膜13を形成する工程と、酸素を含む雰囲気中で熱処理を行い、酸素を金属酸化膜13に透過させて酸化シリコン膜12に拡散させることにより、酸化シリコン膜12に残留する炭素を酸化させる残留炭素酸化工程と、を有することを特徴とする。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有する第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

201 - 220 / 638

[ Back to top ]