Fターム[5F140BD06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiO (1,016) | 材料 (223)

Fターム[5F140BD06]に分類される特許

61 - 80 / 223

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

GaN系電界効果トランジスタ

【課題】低オン抵抗・高耐圧で動作可能なGaN系化合物半導体デバイスを提供する。

【解決手段】基板上に形成されたバッファ層、チャネル層と、前記チャネル層上に形成され、ドリフト層と、前記ドリフト層上に配置されたソース電極およびドレイン電極と、ドリフト層に形成されたリセス部の内表面および前記ドリフト層の表面に形成された絶縁膜と、前記絶縁膜上に形成されたフィールドプレート部を有するゲート電極とを備えたGaN系電界効果トランジスタにおいて、前記ドリフト層は、前記リセス部と前記ドレイン電極との間に、シートキャリア密度が5×1013cm−2以上、1×1014cm−2以下のn型GaN系化合物半導体からなる電界緩和領域を有し、前記ドリフト層の前記電界緩和領域上に形成された前記絶縁膜の厚さが300nm以上であることを特徴とする。

(もっと読む)

半導体装置

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できようにする。

【解決手段】半導体装置は、素子分離領域102により分離された活性領域103を有する半導体基板101と、活性領域103の上に形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極121とを備えている。ゲート絶縁膜111は、シリコン及び酸素を除く第1の元素が拡散している。素子分離領域102は、第1の素子分離膜102Aと、第1の素子分離膜102Aよりもゲート絶縁膜111側に形成され且つ第1の素子分離膜102Aと比べて第1の元素が拡散しにくい第2の素子分離膜102Bとを有している。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】膜組成の制御が容易、かつ、薄膜化が可能なゲート絶縁膜を有した半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、トランジスタが形成される半導体基体1上に、ゲート絶縁膜となる酸化マンガン膜12を形成する工程と、前記酸化マンガン膜12上に、ゲート電極となる導電体膜13を形成する工程と、前記導電体膜13及び前記酸化マンガン膜12を加工し、ゲート電極13及びゲート絶縁膜12を形成する工程と、を具備する。

(もっと読む)

絶縁膜形成方法、及び該方法により得られた酸化膜をゲート絶縁膜として用いる半導体装置

【課題】チャネル部分へのC原子の偏積と酸化膜内へのC原子の蓄積を独立に制御かつ低減する。

【解決手段】半導体基板の表面を熱酸化して、薄い熱酸化膜を成長させ、所望の二酸化ケイ素SiO2絶縁膜厚=前記熱酸化膜の膜厚+堆積したシリコン膜厚の100/44倍、の関係になるようにして求めた膜厚のシリコンを、熱酸化膜の上に堆積する。この堆積したシリコンを熱酸化することにより、所望の膜厚の二酸化ケイ素SiO2絶縁膜を得る。この二酸化ケイ素SiO2絶縁膜の上に、ゲート電極をデポジションしてパターニングし、かつ、ソースドレイン形成をする。

(もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

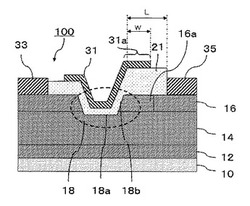

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の侵食を抑制し、FETの故障や不良の発生を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層15を形成する工程と、GaN系半導体層15上に酸化アルミニウムからなるゲート絶縁膜18を450℃以下の成膜温度で形成する工程と、ゲート絶縁膜18の上面に保護膜19を形成する工程、ゲート絶縁膜18を熱処理する工程、及びゲート絶縁膜18をプラズマ処理する工程のいずれか一つと、前記いずれか一つの工程の後に、ゲート絶縁膜18を形成する工程の後のアルカリ溶液を用いた処理を実行する工程と、前記ゲート絶縁膜18上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側から熱酸化膜、CVD酸化膜の2層を積層したゲート絶縁膜を有する半導体装置において、アニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することによる半導体基板等の歪みを低減する。

【解決手段】熱酸化膜とCVD酸化膜との間に、リンガラス膜を形成する。リンガラスは、シリコン酸化膜中にリン(P)を導入して軟化温度(ガラス転移温度)を低くした酸化膜であり、850〜900℃でリフローと呼ばれる流動現象が生じる。900℃以上で行われるCVD酸化膜のアニール処理時には、リンガラス膜がリフロー流動状態となり、熱酸化膜とCVD酸化膜と間で緩衝材として機能する。これによってアニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することが抑制され、ゲート絶縁膜や半導体基板の歪みが低減される。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ100は、基板101と、基板の上に形成されたp型GaN系半導体材料からなるチャネル層104と、チャネル層上に形成され、チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体材料からなる電子供給層106と、電子供給層の一部が除去されて表出したチャネル層104の表面に形成されたゲート絶縁膜111と、ゲート絶縁膜上に形成されたゲート電極112と、ゲート電極を挟んで形成されたソース電極109及びドレイン電極110と、電子供給層106上に形成されたゲート絶縁膜111とは別の絶縁膜であって、電流コラプス低減効果のある第2の絶縁膜113と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、しきい値電圧の低いNチャネルMISトランジスタを有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、NチャネルMISトランジスタの製造方法であって、基板に形成されたP型半導体領域上に、シリコン酸化膜とこのシリコン酸化膜上の金属酸化膜とを含むゲート絶縁膜を形成する工程と、基板を熱処理した状態で、水素ラジカルを含むガスにゲート絶縁膜を暴露する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、を具備することを特徴とする。

(もっと読む)

絶縁膜、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性(SILC、TZDB、TDDBの改善)が得られる絶縁膜、それを用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】主として半導体材料で構成された半導体基板2に接触して設けられ、シリコン、酸素原子、および、これらの原子以外の少なくとも1種の原子Xを含有する絶縁性無機材料を主材料として構成され、水素原子を含むゲート絶縁膜3であって、その厚さ方向の少なくとも一部において、前記原子Xの総濃度をAとし、前記水素原子の濃度をBとしたとき、B/Aが10以下なる関係を満足する領域を有している。これにより、薄膜化した場合でもSBDやSILCが生じ難く、高い絶縁破壊耐性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】高品質のMOS構造に応用可能な、SiC材料の表面にその酸化膜であるSiO2膜が形成されてなる半導体装置を製造する方法を提供する。

【解決手段】SiC材料の表面にその酸化膜であるSiO2膜が形成されてなる半導体装置は、SiC材料の表面にソフトブレークダウン特性を示すSiO2膜を形成し、得られたSiO2膜のソフトブレークダウン特性を改善することにより製造する。具体的には、SiCからあらかじめ形成した熱酸化膜を、比較的高温で酸化種濃度が低い条件で熱処理した酸化膜、あるいは比較的高温で酸化種濃度の低い条件でSiC上に形成した酸化膜を、実質的にSiCで酸化が進行しない温度で酸化種濃度の高い条件下で熱処理すればよい。

(もっと読む)

シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置

【課題】 ゲート絶縁膜等の用途に適した、優れた絶縁特性を有するシリコン酸化膜を形成する。

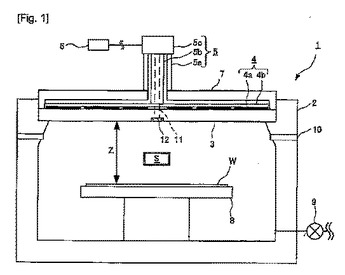

【解決手段】 複数の孔を有する平面アンテナ31により処理容器1にマイクロ波を導入するプラズマ酸化処理装置100において、処理ガス中の酸素の割合を0.1%以上10%以下の範囲内、処理容器1内の圧力を1.3Pa以上266.Pa以下の範囲内に設定し、高周波電源44から、ウエハWを載置する載置台2の電極にウエハWの面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給し、ウエハWにRFバイアスを印加しながら、ウエハWのシリコンに対してプラズマ酸化処理を行う。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁膜のプラズマ処理方法を提供する。

【解決手段】本発明に係るプラズマ処理方法の一形態は、絶縁膜が形成された基板を真空容器内に搬入する工程と、上記真空容器内に供給された処理ガスに300MHz以上2500MHz以下の周波数を有する高周波電力を供給することによりプラズマを生成し、上記プラズマにより、上記絶縁膜を改質する工程と、を含むプラズマ処理方法であって、上記処理ガスは、希ガスと酸素を含む混合ガス、または希ガスと窒素を含む混合ガスであり、上記プラズマは、上記処理ガスが希ガスと酸素を含む混合ガスの場合、上記酸素ガスの流量を1〜1000sccm、上記希ガスの流量を200〜3000sccmとして、上記処理ガスが希ガスと窒素を含むガスの場合、窒素ガスの流量を10〜500sccm、上記希ガスの流量を200〜3000sccmとして生成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

絶縁体の成膜方法

【課題】バリア層上に膜質のよい高誘電率材料の絶縁体が形成され得る、絶縁体の成膜方法を提供すること。

【解決手段】半導体基板の面上に、第1の比誘電率を有する材料を本質的な成分とする第1の絶縁膜を形成する第1の工程と、第1の絶縁膜上に、第1の比誘電率より大きな第2の比誘電率を有する材料を本質的な成分とする第2の絶縁膜を第1の絶縁膜の膜厚より厚く形成する第2の工程と、を具備し、第2の工程が、処理室内に第1の原料ガスを流す工程と、第1の原料ガスをパージする工程と、処理室内に第1の酸化剤を流す工程と、第1の酸化剤をパージする工程と、処理室内に第2の原料ガスを流す工程と、第2の原料ガスをパージする工程と、処理室内に第2の酸化剤を流す工程と、第2の酸化剤をパージする工程とを順次繰り返してなされる。

(もっと読む)

シリコン酸化膜の成膜方法、シリコン酸化膜、半導体装置および半導体装置の製造方法

プラズマ処理装置1のチャンバ2内に、シリコン化合物ガス、酸化性ガス、および希ガスを供給する。マイクロ波をチャンバ2内に供給し、マイクロ波により生成されたプラズマで、被処理基板上にシリコン酸化膜を形成する。希ガスの分圧比は、シリコン化合物ガスと酸化性ガスと希ガスを併せたトータルガス圧の10%以上の割合であって、シリコン化合物ガスと酸化性ガスの有効流量比(酸化性ガス/シリコン化合物ガス)は、3以上11以下とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を活性化するために熱処理をしても閾値の負側へのシフトを抑制した

半導体装置の製造方法を提供する。

【解決手段】基板10上に熱酸化により形成された酸化膜19を介してゲート電極を設けた半導体装置の製造方法であって、基板10上に第1の酸化膜を形成する第1工程と、前記第1の酸化膜を不活性ガス雰囲気にて熱処理をする第2工程と、前記不活性ガスにて熱処理した第1の酸化膜を所定の膜厚となるようにエッチングして得られる第2の酸化膜を形成する第3工程と、前記第2の酸化膜上にゲート電極を形成して熱処理する第4工程と、を有する製造方法である。

(もっと読む)

61 - 80 / 223

[ Back to top ]