Fターム[5F140BD06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiO (1,016) | 材料 (223)

Fターム[5F140BD06]に分類される特許

21 - 40 / 223

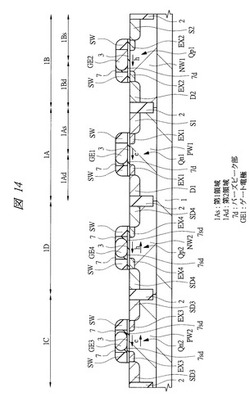

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

炭化ケイ素半導体デバイス

【課題】航空機の配電システムでの使用に際しても、十分に信頼できる炭化シリコンを使用したMOSFETを提供する。

【解決手段】炭化シリコンMOSFETのゲート絶縁膜16を、シリコンからなる第1の層と炭化シリコンからなる第2の層15に貼着することによって、第1の層と第2の層との間に境界面を形成した後、シリコンからなる第1の層の一部又は全部を酸化することにより境界面に炭素クラスターの存在しないゲート絶縁膜16を形成する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明では、低温での成膜処理により、良質なゲート絶縁膜が得られる半導体装置の製造方法を提供することを課題とする。

【解決手段】本発明では上記課題を解決するため、シリコン基板10上に、600℃以下で原子層堆積法により、ゲート絶縁膜の少なくとも一部となる二酸化シリコン膜31を形成する酸化膜形成工程と、二酸化シリコン膜31の表面に対し、酸化処理を行う表面処理工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の端部にトラップされるホットキャリアの数を抑制し、且つ、面積拡大を抑制しつつ高耐圧のMOSトランジスタを作製する。

【解決手段】第1導電型の半導体基板1上に形成したマスクパターン9をマスクとして、第2導電型の一対の第1低濃度拡散領域4と、第1低濃度拡散領域4よりも深くかつ高濃度の第2導電型の一対の第2低濃度拡散領域3と、を形成する。そして、一対の第1低濃度拡散領域4のうちの一方の第1低濃度拡散領域4上から他方の第1低濃度拡散領域4上に亘ってゲート絶縁膜5を形成し、このゲート絶縁膜5上にゲート電極6を形成する。そして、ゲート電極6をマスクとして、第2低濃度拡散領域3よりも高濃度の第2導電型の一対の高濃度拡散領域8を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

21 - 40 / 223

[ Back to top ]