Fターム[5F140BD06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiO (1,016) | 材料 (223)

Fターム[5F140BD06]に分類される特許

41 - 60 / 223

半導体装置、電子装置、半導体装置の製造方法および使用方法

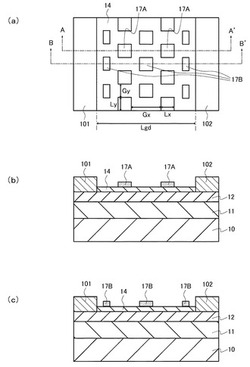

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

電界効果トランジスタ

【課題】電流利得遮断周波数fTの改良された値を示すことのできる、別の形のFETを提供する。

【解決手段】電界効果トランジスタ(FET)は、ベースバイアスを使用して伝導への真性の寄与を低減させ漏れ電流を減少させる種類のものであり、連続した4層102から108を含む。すなわち、p+InSbベース層102、p+InAlSb障壁層104、π真性層106および絶縁SiO2層108である。p+のソースおよびドレイン層110、112が、真性層106にイオン注入される。FETは、エンハンスメントモードMISFET100であり、バイアスによって真性層106にFETチャネルが形成される。絶縁層108の表面はほぼ平坦であり、ゲートコンタクト116を支持する。これによって、ゲート溝の侵入によって引き起こされるチャネルの直線性からのずれをなくし、または減少させ、高い値の電流利得遮断周波数を得ることができるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

チャネルを空乏化する界面電荷を有するゲート絶縁層を備えたトランジスタ及び関連した製造方法

金属−絶縁体−半導体電界効果トランジスタ(MISFET)は、第1の導電型の離間されたソース領域とドレイン領域とをその中に有するSiC層を含む。第1のゲート絶縁層は、SiC層上にあり、SiC層との界面に沿って、ソース領域の多数キャリアと同じ極性の正味の電荷を有する。ゲートコンタクトは、ソース領域とドレイン領域との間のSiC層のチャネル領域の上方の、第1のゲート絶縁層上にある。第1のゲート絶縁層とSiC層との間の界面に沿った正味の電荷は、SiC層内のソース領域とドレイン領域との間のチャネル領域の隣接部分の多数キャリアを空乏化することができ、そのことにより、MISFETの閾値電圧を上昇させ、及び/又は内部の電子移動度を高めることができる。 (もっと読む)

誘電体チャネル空乏層を有するトランジスタ及び関連する製造方法

金属−絶縁体−半導体電界効果トランジスタ(MISFET)は、第1の導電型の離間配置されたソース領域とドレイン領域とを内部に有する半導体層を含む。第1の導電型のチャネル領域が、ソース領域とドレイン領域との間に延びる。ゲートコンタクトが、チャネル領域上にある。誘電体チャネル空乏層が、ゲートコンタクトとチャネル領域との間にある。誘電体チャネル空乏層は、第1の導電型の電荷キャリアと同じ極性を有する正味電荷をもたらし、この正味電荷は、電圧がゲートコンタクトに印加されないとき、チャネル領域の隣接部分から第1の導電型の電荷キャリアを空乏化させることができる。 (もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一半導体チップ内に形成されたNチャネルパワーTDMOSトランジスタとPチャネルパワーTDMOSトランジスタの双方のオン電流に対するオン抵抗の低減を図る。

【解決手段】NチャネルパワーTDMOSトランジスタ用トレンチ4の長辺側とPチャネルTDMOSトランジスタ用トレンチ4の長辺側を45°傾けて形成する。これによりNチャネル側のトレンチ4の長辺側の側壁を(100)面とし、Pチャネル側のトレンチ4の長辺側の側壁を(110)面として、Nチャネル側の電流担体である電子及びPチャネル側の電流担体である正孔の移動度を高くする。移動度を高くすることによりチャネル部分の導電率を高める。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を拡大し、駆動電流の増大を図ることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2に埋め込まれた埋込み絶縁膜3により絶縁分離された活性領域5と、活性領域5上に形成されたゲート絶縁膜6を介して当該活性領域5を跨ぐように形成されたゲート電極7と、ゲート電極7を挟んだ両側の活性領域5にイオン注入することによって形成されたソース領域8及びドレイン領域9とを備え、活性領域5に溝部10が設けられて、この溝部10の内側にゲート絶縁膜6を介してゲート電極7の一部が埋め込まれてなるトレンチ型のチャネル構造を有し、活性領域5の両側面に凹部11が対向して設けられて、これら凹部11の間に幅狭部12が形成されることによって、少なくとも溝部10の底面と幅狭部12との間に当該幅狭部12よりも幅広となるチャネル領域13が形成されている。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

超高品質シリコン含有化合物層の形成方法

【課題】ALDがCVDに比べて優れたコンフォーミティ(coformality)、成膜速度及び均一性を備えた気相堆積方法を提供する。

【解決手段】シリコンナイトライド層を含む、超高品質シリコン含有化合物層を形成するため、複数の順次的なステップ140が、反応チャンバー中で実施される。好ましい実施態様において、シリコン前駆物質としてトリシランを用いて、シリコン層が基板上に堆積100される。シリコン前駆物質は、反応チャンバーから除去される110。その後、シリコンナイトライド層が、シリコン層を窒化すること120によって形成される。窒素反応物質は、反応チャンバーから除去される110。これらのステップ100、110、120及び130を繰り返すことによって、所望の厚さのシリコンナイトライド層が形成される。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】低いコンタクト抵抗を有し、かつ、オン抵抗の増大を回避できて高いチャネル移動度を維持できるノーマリオフ動作の電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタは、AlGaN障壁層6の薄層部6aは、第2のGaN層4のV欠陥13およびV欠陥13に連なる第3のGaN層5の非成長領域G1上に形成されているので、エッチングを行うことなく平坦部6bよりも薄くできる。よって、エッチングダメージがチャネル移動度を低下させることがなく、オン抵抗の増大を回避できる。

(もっと読む)

GaN系半導体素子およびその製造方法

【課題】SiO2からなるゲート絶縁膜を常圧CVDによって形成することで、十分なノーマリオフ特性が得られるGaN系半導体素子およびその製造方法を提供する。

【解決手段】基板11上にバッファ層13を介して積層されたp型のGaN系化合物半導体からなるチャネル層14とゲート電極Gとの間にゲート絶縁膜17が形成されたGaN系半導体素子1において、ゲート絶縁膜17が、常圧CVD法により成膜されたSiO2膜である。常圧CVD法により成膜されたSiO2膜は、Si−H結合や未結合手の発生が抑制された高品質のSiO2膜である。このようなSiO2膜により、GaN系半導体素子のしきい値の制御に及ぼす悪影響も抑制されるので、十分なノーマリオフ特性が得られる。

(もっと読む)

成膜方法、ゲート電極構造の形成方法及び処理装置

【課題】シリコン層の表面をケミカル酸化膜で保護した状態で低酸素分圧酸化を行うことにより、膜厚の面内均一性が高くて且つ欠陥の少ない極めて薄い界面酸化膜を得ることが可能な成膜方法を提供する。

【解決手段】被処理体Wのシリコン層の表面に、ゲート絶縁膜との間に介在される界面酸化層を形成する成膜方法において、シリコン層をケミカル洗浄処理することによってケミカル酸化膜を形成するケミカル酸化膜形成工程と、ケミカル酸化膜の形成された被処理体に対して酸素分圧が0.2〜2Paの範囲内の雰囲気中で熱処理を施すことにより界面酸化膜を形成する熱処理工程とを有する。これにより、シリコン層の表面をケミカル酸化膜で保護した状態で低酸素分圧酸化を行うことで、膜厚の面内均一性が高くて且つ欠陥の少ない極めて薄い界面酸化膜を得る。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

電界効果トランジスタ

【課題】大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層13の表面領域に形成されたソース18s及びドレイン18dと、半導体活性層13上にゲート酸化膜14を介して形成されたゲート電極15と、ゲート電極15とドレイン18dの間の半導体活性層13上に形成されたパッシべーション膜20とを備える。電界効果トランジスタ10では、パッシベーション膜20を構成する二酸化シリコンの膜質が、ゲート酸化膜14を構成する二酸化シリコンの膜質よりも密度が粗である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

補償型ゲートMISFET及びその製造方法

低いゲートリークを有する例えばGaNトランジスタなどのMISFETが提供される。一実施形態において、ゲートコンタクトの下且つバリア層の上に、補償型のGaN層を有することで、ゲートリークが低減される。他の一実施形態において、ゲートコンタクトの下且つバリア層の上に半絶縁性の層を用いることによって、ゲートリークが低減される。  (もっと読む)

(もっと読む)

41 - 60 / 223

[ Back to top ]