Fターム[5F140BD06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | SiO (1,016) | 材料 (223)

Fターム[5F140BD06]に分類される特許

121 - 140 / 223

埋込方法、半導体素子製造方法および半導体素子

【課題】メサ形状である第1の材料層の周囲に第2の材料を空隙なく平坦に埋め込むことができる埋込方法、半導体素子製造方法、および、メサ形状である第1の半導体層の周囲に第2の半導体が空隙なく平坦に埋め込まれた半導体素子を提供すること。

【解決手段】本発明にかかる埋込方法は、基板上に形成された第1の材料層上にエッチングマスクを形成するマスク形成工程と、エッチングマスク周縁が所定幅分突出するように第1の材料層をメサ形状にドライエッチングするエッチング工程と、エッチング工程後に第2の材料によってメサ形状周囲を選択的に埋め込む埋込工程と、エッチングマスクを除去するマスク除去工程と、を含むことを特徴とする。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の製造方法、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難く、高い絶縁破壊耐性(TZDB、TDDBの改善)が経時的に得られるゲート絶縁膜、かかるゲート絶縁膜の製造方法および評価方法、さらに、このゲート絶縁膜を用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】ゲート絶縁膜3は、半導体基板(基材)2上に化学的気相成膜法を用いて成膜され、平均厚さが10nm以下のものであり、シリコン、酸素原子および水素原子で構成され、その密度が2.5g/cm3以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難いゲート絶縁膜、かかるゲート絶縁膜の評価方法を提供する。

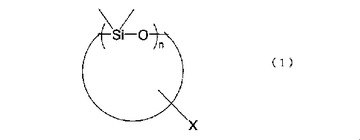

【解決手段】ゲート絶縁膜3は、下記一般式(1)で表される構造を有しており、下記一般式(1)で表される構造中のnが3または4であるものの総数をAとし、nが5以上であるものの総数をBとしたとき、{A/(A+B)}×100が1.2%以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

[式中、nは2以上の整数を表す。また、Xは水素原子または水酸基を表す。]

(もっと読む)

MIS構造を内蔵するHEMT

【課題】 ノーマリオフで動作するMIS構造を有するHEMTを提供すること。

【解決手段】 HEMT10は、ドレイン電極に電気的に接続するドレイン領域32と、ソース電極に電気的に接続するソース領域34と、ドレイン領域32とソース領域34の間に形成されている第1半導体領域22と、第1半導体領域22の表面の一部にゲート絶縁膜42を介して対向しているゲート電極42を有するMIS構造40と、第1半導体領域22の表面の残部に接しているとともに第1半導体領域22のバンドギャップよりも広いバンドギャップを有する第2半導体領域24を有するヘテロ構造を備えている。ドレイン領域32とソース領域34は、MIS構造40とヘテロ構造を直列に配置した構造で接続されている。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

半導体装置及びその製造方法

【課題】FinFETのチャネル上縁部付近での電界集中を抑えると共に、製造の歩留りを高めた半導体装置を提供する。

【解決手段】FinFETは、シリコン基板11の表面に堆積され、ソース拡散層24a、ドレイン拡散層24b、及び、チャネル領域を形成するシリコン層14と、シリコン基板11上に素子分離層12を介して堆積され側部ゲート絶縁膜16を介してチャネルの側面に対向する一対の第1電極部分18と、頂部ゲート絶縁膜15を介してチャネルの頂面に対向し、且つ、第1電極部分18の頂部に接する第2電極部分19とを有するゲート電極とを有する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体ウェーハおよびその製造方法

【課題】安定した原子レベルの平坦面(テラス)を有する半導体ウェーハおよびその製造方法を提供する。

【解決手段】半導体の表面に絶縁膜が形成された半導体ウェーハであって、半導体と絶縁膜の界面が、平坦面(テラス)が結晶面に平行な面で構成される段差(ステップ)構造を有し、界面の任意の3μm×3μmの領域を、原子間力顕微鏡(AFM)の測定領域とした場合に、この測定領域において、段差に概ね垂直方向の、概ね0.3μm間隔の10本の測線に沿って測定された平坦面の幅(テラス幅)の測定値の90%以上が50nm以上であり、測定領域において、段差に概ね垂直方向の10本の測線に沿って測定された前記段差の高さ(ステップ高さ)の測定値の90%以上が1原子層分の高さであることを特徴とする半導体ウェーハおよびその製造方法。

(もっと読む)

半導体装置

【課題】電子供給層と絶縁層との間の界面準位を低減させ、リーク電流やドレイン電流のコラプス等の抑制を可能とすること。

【解決手段】本発明は、基板(10)上に設けられたGaN電子走行層(12)と、電子走行層(12)上に設けられ2次元電子ガス(13)を電子走行層(12)に生成するAlGaN電子供給層(14)と、電子供給層(14)上に設けられたGaN層(20)と、GaN層(20)との間に絶縁膜(32)を介し設けられたゲート電極(34)と、を具備する半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低減され、優れた高周波特性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、ゲート絶縁膜と、ゲート電極と、ドレイン領域およびソース領域と、基板上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上または上方に形成された第2の層間絶縁膜とを備えている。ドレイン領域はゲート電極とゲート長方向に離れて形成されている。第1の層間絶縁膜上には、ゲート電極とドレイン領域との間に設けられたフィールドプレートと、ゲート電極に接続され、ソース領域を跨いで延びる金属膜とが形成され、第2の層間絶縁膜上にはゲート電極を跨いでフィールドプレートの上方およびソース領域の上方を被い、フィールドプレートに接続された金属膜17bが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート長の異なるMISFET間のしきい値のばらつきを抑制した半導体装置及びその製造方法を提供すること。

【解決手段】 半導体基板100の第一及び第二領域112、113上にゲート絶縁膜103及びダミー層111を形成し、ダミー層111を加工して第一のダミーゲート114と第一のダミーゲート114よりゲート長の長い第二のダミーゲート115を形成。第一及び第二のダミーゲート114、115を利用してダミー絶縁層116を形成し、第一及び第二のダミーゲート114、115を除去してダミー絶縁層116に第一と第二の開口部117、118を形成し、第一の開口部117全体及び第二の開口部118の一部に第一の導電膜107を形成し、第二の開口部118に第一の導電膜107とは異なる仕事関数の第二の導電膜108を、第一領域112上に第一のMISFET105、第二領域113上に第二のMISFET106とを形成する。

(もっと読む)

パワーMOSFET及び同パワーMOSFETを有する半導体装置及び同パワーMOSFETの製造方法

【課題】UIS特性を向上させたパワーMOSFET及び同パワーMOSFETを有する半導体装置及び同パワーMOSFETの製造方法を提供する。

【解決手段】半導体基板上に設けられた第1導電型の不純物を含有するウェル領域に、所定間隔を空けて第2導電型の不純物を添加して形成されたソース領域及びドレイン領域を有し、ソース領域とドレイン領域との間におけるウェル領域の表面に絶縁膜を介してゲート電極が設けられたパワーMOSFETを有する半導体装置を製造する際に、ウェル領域をエピタキシャル層により形成し、このエピタキシャル層に不純物濃度が異なる第1導電型の不純物層を形成することとした。

(もっと読む)

絶縁膜形成方法、絶縁膜形成装置、半導体装置の製造方法、および半導体装置並びにシリコンカーバイドの基板の表面処理方法

【課題】 シリコンカーバイド(SiC)等を用いた半導体デバイスに適用しうる絶縁膜形成において、低温での化学的な酸化膜形成を効果的に行なうための、前処理としての表面処理方法を提供する。

【解決手段】 水素を含む雰囲気中で基板10の表面を加熱した後、その表面を酸化性溶液22中に浸漬し、または酸化性溶液を噴霧し、あるいは酸化性溶液の蒸気に曝す工程を有する。これにより、酸化性溶液22と接触する基板10の表面における反応性の向上が期待でき、その基板10の表面に極薄膜であっても高性能な絶縁膜が形成される。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法および携帯電子機器

【課題】キンク効果を抑制できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】シリコン基板101に形成された素子分離領域102とその素子分離領域102以外の領域との境界を跨ぐように、シリコン基板101上にゲート絶縁膜103を介してゲート電極104が形成されたMOSトランジスタを備える。上記素子分離領域102とその素子分離領域102以外の領域との境界の段差領域120におけるゲート絶縁膜103の膜厚を、その段差領域120以外の領域におけるゲート絶縁膜103の膜厚に対して65%〜100%とする。

(もっと読む)

簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体

【課題】 簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体を提供すること。

【解決手段】 ゲート誘電体の下にあるチャネル領域内の応力を強化するために、新しいデュアル応力ライナ構成が用いられる、完全にシリサイド化されたゲート電極を有するnFETを含む半導体構造体が提供される。新しいデュアル応力ライナ構成は、nFETの完全にシリサイド化されたゲート電極の上面と実質的に同一平面にある上面を有する第1の応力ライナを含む。本発明によると、第1の応力ライナは、完全にシリサイド化されたゲート電極を含むnFETの上には存在しない。代わりに、本発明の第1の応力ライナは、完全にシリサイド化されたゲート電極を有するnFETを部分的に包み込む、すなわちその両側を囲む。第1の応力ライナのものと反対の極性を有する(すなわち、反対の応力型の)第2の応力ライナが、第1の応力ライナの上面上及び完全にシリサイド化されたFETを含むnFETの上に配置される。本発明によると、第1の応力ライナは引張応力ライナであり、第2の応力ライナは圧縮応力ライナである。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 窒化物半導体層に形成される制御電極のショットキ特性の向上、高耐圧化、周波数分散の抑制を可能とし、スレッショホールド電圧の制御が容易なノーマリーオフ動作を実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 基板上に、第1の窒化物半導体層と微結晶構造からなる第2の窒化物半導体層を形成し、制御電極形成領域にマスク膜を形成する。マスク膜を用いて露出する第1の窒化物半導体層上に、第3の窒化物半導体層と微結晶構造からなる第4の窒化物半導体層を形成する。マスク膜を除去し、第2の窒化物半導体層上に制御電極を形成する。

(もっと読む)

p型チャネルを含む炭化シリコンスイッチングデバイスおよびその形成方法

炭化シリコン内にpチャネルMOSデバイスを形成する方法は、炭化シリコン層内にn型ウェルを形成すること、および炭化シリコン層の表面のn型ウェル内にp型領域を形成するために、p型ドーパントイオンを注入することを含み、p型領域は、p型領域に隣接したn型ウェル内にチャネル領域を少なくとも部分的に画定する。チャネル領域内にしきい値調整領域が形成される。注入されたイオンは、不活性雰囲気で、1650℃よりも高温でアニールされる。チャネル領域上にゲート酸化物層が形成され、ゲート酸化物層上にゲートが形成される。炭化シリコンベースのトランジスタは、炭化シリコン層と、炭化シリコン層内のn型ウェルと、炭化シリコン層の表面のn型ウェル内のp型領域であって、p型領域に隣接したn型ウェル内にチャネル領域を少なくとも部分的に画定するp型領域とを含む。チャネル領域内にはしきい値調整領域があり、このしきい値調整領域は、p型ドーパントを、約1×1016cm-3から約5×1018cm-3のドーパント濃度で含む。このトランジスタはさらに、チャネル領域上のゲート酸化物層と、ゲート酸化物層上のゲートとを含む。このトランジスタは、チャネル領域内において、ゲート電圧−25Vで約5cm2/V−sを超える正孔移動度を示すことができる。  (もっと読む)

(もっと読む)

静電気放電保護素子および半導体装置

【課題】半導体集積回路のESD保護素子としての性能を向上させるとともに、ESD保護素子形成領域を小さくすることができる静電気放電保護素子を得ること。

【解決手段】半導体基板1上に形成されたゲート絶縁膜12、ゲート電極13およびサイドウォール膜14からなるゲート構造11と、ゲート構造11の両側に形成される高濃度不純物拡散層からなるソース領域15およびドレイン領域16と、ソース領域15とドレイン領域16のゲート構造11側に形成される低濃度不純物拡散層からなるエクステンション部17と、ソース電極と、ドレイン電極と、を備え、ゲート電極とソース電極が接地された複数の電界効果型トランジスタによって構成されるマルチフィンガタイプの静電気放電保護素子において、ソース電極とゲート電極13との間、およびドレイン電極とゲート電極13との間の高濃度不純物拡散層内に、低濃度不純物拡散層からなる抵抗領域18を備える。

(もっと読む)

実効仕事関数を調整するための方法

【課題】本発明は、様々なトランジスタタイプの金属ゲート電極の実効仕事関数及び閾値電圧を、簡便で、再生可能でまた効率的な方法で制御することができるMOSFETデバイスを製造する方法を提供すること。

【解決手段】本発明は、MOSFET、FinFET、若しくはメモリーデバイスにおけるゲートを作製するにあたり、半導体基板上に、(予め)決定された移動度、リーク、及び/又はEOT(酸化膜換算膜厚)の仕様を満たす誘電体材料からなる少なくとも一層を成長させ、

上記ゲート電極を形成する前に、上記少なくとも一層の誘電体層とゲート電極との間の界面に、ランタンハフニウム酸化物材料を含む若しくはこれからなる、好ましくはLa2Hf2O7からなる界面層を成長させ、上記界面層に接触する誘電体材料からなる少なくとも一層を、上記界面層材料と相違させることを特徴とする。

金属ゲート電極、ゲート誘電体及び界面層を備える新たなMOSFETを開示している。その製造方法、及びその応用も提供する。

(もっと読む)

121 - 140 / 223

[ Back to top ]