Fターム[5F140BD11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702)

Fターム[5F140BD11]の下位に属するFターム

Fターム[5F140BD11]に分類される特許

101 - 120 / 1,414

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リーク電流および閾値を低減させるゲート絶縁膜を提供する。

【解決手段】図1に示すように、半導体基板1上に、ゲート絶縁膜3を形成するゲート絶縁膜形成工程と、ゲート絶縁膜3上に、ゲート電極4を形成するゲート電極形成工程と、を備え、ゲート絶縁膜形成工程は、第1金属の酸化膜あるいは酸窒化膜を、成膜する第1の成膜工程と、第1金属の酸化膜あるいは酸窒化膜上に第2金属または、その酸化物を成膜する第2の成膜工程と、第2金属を第1金属の酸化膜中に拡散させるために熱処理する熱処理工程の3工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

絶縁膜の製造方法

【課題】質量密度の高い絶縁膜の製造方法を提案すること。

【解決手段】絶縁膜の製造方法は、基板の上に絶縁膜を形成するステップと、その絶縁膜を処理するステップとを備えている。絶縁膜は、SiとOとを含んでおり、たとえばSiO2膜である。第2のステップでは、絶縁膜の温度を551℃以上574℃以下として、活性状態の希ガスと活性状態の酸素とを絶縁膜に供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

ゲルマニウム酸化膜の形成方法および電子デバイス用材料

【課題】Ge基板と絶縁膜との界面に、良好なGe酸化膜を形成する。

【解決手段】上面に絶縁膜(High−k膜)32が積層されたGe基板31の絶縁膜32の表面から、酸素原子含有ガスを含む処理ガスのプラズマを照射する。絶縁膜32越しにGe基板31を酸化させて、絶縁膜32とGe基板31との界面にGe酸化膜33を形成する。絶縁膜32がGe酸化膜33に対して保護膜として機能し、形成されたGe酸化膜33の劣化を防ぐ。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

ISFETおよびISFETアレイ

【課題】センサ感度を向上したISFETおよびこのISFETセルを適用したISFETアレイを提供する。

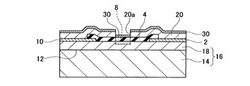

【解決手段】第1導電型を有する半導体基板10と、半導体基板10上に配置され、第1導電型と反対導電型の第2導電型を有するウェル領域12と、ウェル領域12上に配置され、第1導電型を有するソース領域14およびドレイン領域16と、ウェル領域12上に配置されたゲート絶縁膜18と、ゲート絶縁膜18上に、ドレイン領域16に隣接して配置されたトランスファゲート電極20と、ゲート絶縁膜18に接触する液体試料26と、液体試料26中に配置された参照電極24とを備えるISFET2およびこのISFETセルを適用したISFETアレイ4。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

トランジスタ及びその製造方法

【課題】駆動電流を向上したnMOSトランジスタを備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の素子領域101の上にゲート絶縁膜111を介在させて形成されたゲート電極112と、素子領域101におけるゲート電極112の両側方に形成され、n型不純物及び炭素を含むソースドレイン領域122とを備えている。ソースドレイン領域122を構成するシリコン及びソースドレイン領域122に含まれる炭素の少なくとも一方は、主同位体よりも質量数が大きい安定同位体の存在比が、天然存在比よりも高い。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

エッチング方法、半導体装置の製造方法及びエッチング装置

【課題】エッチング水溶液を用いたエッチング速度の向上したエッチング装置を提供する。

【解決手段】本明細書に開示するエッチング装置10は、放射線11をエッチング水溶液20に照射する放射線源12と、放射線11が照射されるエッチング水溶液20を収容するエッチング槽13と、放射線源12から照射される放射線11を反射して、放射線11をエッチング水溶液20に照射する反射部とを備える。エッチング槽13は、放射線11を透過する放射線窓15を有し、放射線窓15の内側には、被エッチング物30の表面を水酸基によって官能化する活性種のエッチング水溶液20からの生成を促進する触媒層16aが配置される。

(もっと読む)

電界効果型トランジスタ、電界効果型トランジスタの製造方法、固体撮像装置、及び電子機器

【課題】 ゲート電極の微細化が可能な電界効果型トランジスタを提供する。

【解決手段】 本開示に係る電界効果型トランジスタは、基板10と、基板10上に形成され、フィン領域13と該フィン領域13の両端にそれぞれ形成されるソース領域14とドレイン領域15とを有する半導体層と、フィン領域13の少なくとも2面の一部と接する凸部171を有するゲート電極17と、を備える。

(もっと読む)

101 - 120 / 1,414

[ Back to top ]