Fターム[5F140BD11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702)

Fターム[5F140BD11]の下位に属するFターム

Fターム[5F140BD11]に分類される特許

61 - 80 / 1,414

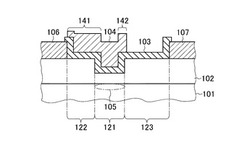

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置

【課題】ゲート絶縁膜を形成する際に、界面準位を低減しつつ、EOTのさらなる低減が実現可能な金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置を提供すること。

【解決手段】単結晶領域102を有する基板101上に、金属膜であって、該金属膜の酸化物の誘電率が酸化シリコン膜よりも高く、かつ金属膜の酸化物が単結晶領域102とエピタキシャル関係を有する金属膜103を、単結晶領域102と金属膜103とが界面反応しない基板温度で形成する(図1(b))。金属膜103が形成された基板101を、上記界面反応しない基板温度で、単結晶領域102と金属膜103とが界面反応しない酸素分圧の酸素ガス雰囲気に暴露する(図1(c))。酸素ガス雰囲気に暴露された基板103を、上記酸素分圧の酸素ガス雰囲気に保持し、金属膜の酸化物である金属酸化物高誘電体膜が結晶化する基板温度で熱処理する(図1(d)。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

61 - 80 / 1,414

[ Back to top ]