Fターム[5F140BD11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702)

Fターム[5F140BD11]の下位に属するFターム

Fターム[5F140BD11]に分類される特許

141 - 160 / 1,414

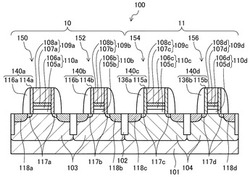

半導体装置およびその製造方法

【課題】用途によって異なるしきい値電圧を有するトランジスタを有する半導体装置、及び工程数の増加を抑えた当該半導体装置を製造する方法を提供する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1のゲート絶縁膜110aと、第1のゲート絶縁膜110a上に形成された第1のゲート電極109aと、第1のゲート絶縁膜110aの側面上及び第1のゲート電極109aの側面上に形成された第1のサイドウォール絶縁膜140aとを有する第1導電型の第1のMISFET150を備えている。第1のサイドウォール絶縁膜140aの少なくとも一部には、第1のゲート絶縁膜110aに正または負の固定電荷を誘起するための元素が含まれている。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、トランジスタの特性を低下させることなく高い密度のドレイン電流が実現できるようにする。

【解決手段】主表面を(0001)面とした第1窒化物半導体からなるチャネル層101と、チャネル層101の上に形成された第1窒化物半導体より大きなバンドギャップエネルギーの窒化物半導体からなる第1障壁層102と、ゲート電極104が形成されたゲート形成領域121を挟んだソース形成領域122およびドレイン形成領域123の第1障壁層102の上に形成され、第2窒化物半導体より大きなバンドギャップエネルギーの第3窒化物半導体からなる第2障壁層105および第3障壁層106と、第2障壁層105および第3障壁層106の上に形成された第2窒化物半導体からなる第4障壁層107および第5障壁層108とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

半導体装置の製造方法、および半導体装置

【課題】GaNを有する窒化物の上にマイクロ波プラズマを用いてゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】GaN層13,AlGaN層14aが積層されたFET構造と、フィールド酸化膜15とゲート電極20との間にかけて、形成されたゲート絶縁膜19bを備える。ゲート絶縁膜19bは、アルミナ24aとシリコン酸化膜24bから構成される二層構造とする。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の特性を劣化させることなく、浅い接合の半導体装置を提供する。

【解決手段】まず、半導体基板上に、ゲート絶縁膜を形成する(s100)。次いで、ゲート絶縁膜上にゲート電極を形成する(s200)。次いで、ゲート電極を形成する工程(s200)の後、第一アニール工程を行う(s300)。次いで、第一アニール工程(s300)の後、ゲート電極の両側における半導体基板に、ポケット領域およびエクステンション領域を構成する不純物注入を行う(s400)。その不純物注入を行う工程(s400)の後、第二アニール工程として、最高アニール温度が1000℃以上で、アニール時間が100ミリ秒以下であるアニールを行う(s700)。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

電界効果型トランジスター

【課題】ダイヤモンドFETにおいて、ドレイン電流特性を改善すること。

【解決手段】ダイヤモンド結晶層1の上に、高濃度ホウ素ドープダイヤモンド薄膜層102を成長する(図1(a))。次に、ソース電極およびドレイン電極として、Ti層131A、131B、Au層132A、132Bを順に蒸着する(図1(b))。次に、400℃でアニールを行いTiをダイヤモンドと反応させて、TiC層133A、133Bを形成する(図1(c))。最後に、ゲート部にAl2O3膜141を形成し、その上にAlゲート電極42を蒸着する(図1(d))。作製したダイヤモンドFETのドレイン電流特性は、ゲート電圧−3Vにおける最大ドレイン電流密度が600mA/mmとなり、従来技術による場合の約6倍に増加した。温度依存性に関しては、従来技術では室温から150℃付近でドレイン電流密度は急激に減少したが、本発明では900℃まで安定して動作した。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

141 - 160 / 1,414

[ Back to top ]