Fターム[5F140BF18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 金属 (2,560) | 金属シリサイド (1,436)

Fターム[5F140BF18]の下位に属するFターム

複数種からなる金属シリサイド (110)

Fターム[5F140BF18]に分類される特許

21 - 40 / 1,326

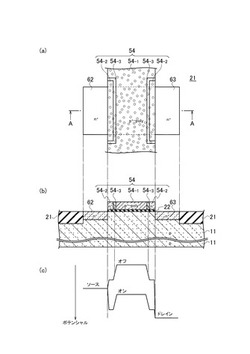

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能する第1導電型の半導体層11、チャネル領域を囲み、半導体層11に活性領域を定義する素子分離絶縁膜21、活性領域の一方に設けられた第2導電型の第1主電極領域62、活性領域の他方に設けられた第2導電型の第2主電極領域63、活性領域の表面のゲート絶縁膜22、多結晶シリコン層を含んで、ゲート絶縁膜22の上に設けられたゲート電極54を備える。多結晶シリコン層は、第1主電極領域62,第2主電極領域63に接する部分は第2導電型の第1多結晶シリコン領域54-2、チャネル領域と素子分離絶縁膜21との境界領域の上部は第1導電型の第2多結晶シリコン領域54-1である。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

炭化ケイ素半導体装置の製造方法

【課題】炭化ケイ素(000−1)面にウェット雰囲気で酸化されたゲート絶縁膜の上に、ポリシリコンを不活性ガスを使用した減圧CVD法で成膜しても、界面準位密度の増加を抑制し、MOS界面特性の劣化を防止して、炭化ケイ素半導体装置の品質を高める。

【解決手段】炭化ケイ素半導体の(000−1)面から0°ないし8°傾いた面からなる半導体領域上に接するようにゲート絶縁膜を形成し、減圧CVD法を用いて、ゲート絶縁膜上に接するようにポリシリコンのゲート導電膜を成膜する際、不活性ガスを供給しながら安定化させる目標炉内温度を450℃以上550℃以下にするとともに、原料ガスを注入しながらポリシリコンのゲート導電膜の生成を行う工程、さらには、このゲート導電膜の生成終了後、原料ガスを不活性ガスに置換する工程を含め、炉内温度を一貫してこの目標炉内温度に維持した。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

21 - 40 / 1,326

[ Back to top ]