Fターム[5F140BG32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644) | イオン注入 (445)

Fターム[5F140BG32]に分類される特許

161 - 180 / 445

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性に優れた微細な半導体装置を提供する。

【解決手段】半導体基板と、半導体基板に形成されたトレンチ内の絶縁体からなる素子分離領域と、このトレンチ内の絶縁体に囲まれた半導体領域およびその上に形成された単結晶シリコン層を含む活性領域と、この単結晶シリコン層上に形成されたゲート絶縁膜と、前記活性領域を跨ぐようにゲート絶縁膜上に設けられたゲート電極と、このゲート電極の両側の、前記活性領域に設けられた拡散層と、を有する半導体装置。

(もっと読む)

半導体装置の構造および製造方法

【課題】STI領域の絶縁膜掘り下げにより形成される幅30nm以下の拡散層が配されているFinFETにおいて、寄生抵抗を低減した構造及びその製造方法を提供する。

【解決手段】STI領域105に挟まれ、素子分離領域上方に突き出た幅30nm以下の半導体層にソース及びドレイン領域となる拡散層104が形成されており、ソース及びドレイン領域間のチャネル領域を跨ぐゲート電極を有する凸型Fin構造の電界効果トランジスタであって、前記ソース及びドレイン領域となる拡散層側壁にサイドウォール110b、該サイドウォールに挟まれた拡散層上面に選択エピタキシャル成長シリコン層111、及び該選択エピタキシャル成長シリコン層に接続されるコンタクトプラグ115を有することを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】製造コストを抑えつつ、ソース又はドレインと基板との間に生じる接合容量を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1にMOSトランジスタを形成する半導体装置の製造方法であって、シリコン基板1に素子分離膜3を形成する工程と、シリコン基板1上にゲート絶縁膜5を介してゲート電極7を形成する工程と、ゲート電極7と離間して、シリコン基板1上から素子分離膜3上にかけて引出電極9を形成する工程と、ゲート電極7と引出電極9とにより平面視で挟まれた領域のシリコン基板1に不純物を導入してS/D層11を形成する工程と、S/D層11上から引出電極9の少なくとも側面にかけてシリサイド23を形成する工程と、を含む。

(もっと読む)

半導体装置、およびその製造方法

【課題】応力膜によるチャネル領域への歪み効果を向上させる形状の半導体基板を有し、かつ十分な深さのソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板と、半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板の前記ゲート電極の両側の前記ゲート電極から離間した領域に凹部を形成する工程と、前記凹部の底面および側面からほぼ同じ深さまで前記半導体基板に導電型不純物を注入する工程と、前記凹部の底面および側面上に、前記半導体基板内の前記ゲート電極下のチャネル領域に歪みを与えて前記チャネル領域における電荷移動度を向上させる応力膜を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の製造において、細線化したゲート電極上のシリサイドにおける凝集の防止および当該シリサイドの薄膜化を両立する。

【解決手段】NMOSトランジスタのゲート電極12並びにソース・ドレイン領域15の上部、およびPMOSトランジスタのゲート電極22並びにソース・ドレイン領域25には、それぞれNiシリサイド膜12s,15s,22s,25sが自己整合的に形成されている。Niシリサイド膜12s,15s,22s,25sは、NiおよびSiを主成分とし、化学量論組成がNiSiあるいはNiSi2である。但しそれらはPt,V,Pd,Zr,Hf,Nbのうち1以上の元素を合計で10at%未満の固溶量で含んでいる。

(もっと読む)

nチャネルMOSトランジスタおよびその製造方法、半導体装置

【課題】ゲートファーストプロセスで形成できる、金属化合物をゲート電極パターンとして使うnチャネルMOSトランジスタにおいて、pチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物に対し、前記nチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物の仕事関数差を増大させる。

【解決手段】nチャネルMOSトランジスタは、p型シリコン活性領域上にゲート絶縁膜を介して形成された導電性金属窒化物よりなるゲート電極パターンと、前記p型シリコン活性領域中、前記ゲート電極パターンの一方および他方の側にそれぞれ形成されたn型のソースおよびドレイン領域と、を含み、前記導電性金属窒化物は、SiおよびV族元素を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域における歪みを適正に増大させ、キャリア注入速度を向上させて、近時における更なる狭チャネル化にも対応したトランジスタ特性の大幅な向上を可能とする信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極101の側面に、自身は膨張性を有する応力膜からなる第1のサイドウォール111と、第1のサイドウォール111上にこれに比して応力の小さい膜からなる第2のサイドウォール112とが形成されており、半導体層、例えばSiC層104が第2のサイドウォール112により第1のサイドウォール111から離間する。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に格子歪を導入したMISFETを有する半導体装置の製造方法に関し、効率よくチャネル領域に格子歪みを導入してMISFET特性を向上しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、ポリシリコンよりなるゲート電極26nを形成し、ゲート電極26nの側壁部分にサイドウォールスペーサ28,38,40を形成し、ゲート電極26nの上端部がサイドウォールスペーサ28,38,40の上端部よりも低くなるように、ゲート電極26nをエッチングし、ゲート電極26nの一部をアモルファス化しゲート電極26nを覆うようにキャップ絶縁膜を形成し、アモルファス化したゲート電極26nを再結晶化するための熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域をシリサイド化しても、リーク電流を可及的に抑えることを可能にする。

【解決手段】半導体領域7を有するシリコン基板2と、半導体領域に離間して形成されたソース/ドレイン領域11a、15a、11b15bと、ソース領域とドレイン領域との間の半導体領域上に形成された絶縁膜9aと、絶縁膜上に形成されたゲート電極10aと、ゲート電極の側部に形成された側壁絶縁膜13aと、第1ソース/ドレイン領域上に形成され、少なくとも{111}面となる表面を有する単結晶シリコン層17a、17bと、少なくとも単結晶シリコン層の{111}面上に形成され、かつ側壁絶縁膜に接する部分を有し、この部分と単結晶シリコン層との界面が単結晶シリコン層の{111}面であるNiSi層21a、21bと、NiSi層に接する第1のTiN膜23a、23bと、を有する第1のMOSFETと、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】ホウ素(B)のゲート絶縁膜の突き抜けや金属シリサイド膜による不純物の吸収によって生じるポリシリコン膜中の不純物の空乏化を防止する。

【解決手段】半導体装置100は、ゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14とを備える。ゲート電極14は、ドープドポリシリコン膜21a、21b、21cと、金属シリサイド膜22aとを備えている。ドープドポリシリコン膜21a、21cは、第1の不純物を含んでおり、ドープドポリシリコン膜21bは、反対の導電型を有する第2の不純物を含んでいる。これにより、ポリシリコン中の不純物の拡散工程やその後の熱負荷工程において、第2のドープドポリシリコン膜中の不純物の過度な拡散が抑制され、金属シリサイド膜が不純物を吸収することによるポリシリコン膜中の不純物の空乏化が防止される。

(もっと読む)

半導体装置

【課題】チャネル領域に歪みを与えてキャリア移動度を向上させつつ、ソース・ドレイン領域またはソース・ドレイン領域とシリサイド層の界面における電気抵抗の増加を抑えることのできる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、

前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板の前記ゲート電極の下方に形成されたチャネル領域と、前記チャネル領域の両側に形成され、前記チャネル領域に歪みを与える第1の結晶を含むソース・ドレイン・エクステンション領域と、前記ソース・ドレイン・エクステンション領域に隣接した前記チャネル領域と反対側の領域に形成され、内部の電気抵抗が前記第1の結晶よりも小さい性質と、シリサイドとの界面における電気抵抗が前記第1の結晶よりも小さい性質との少なくともいずれか一方を有する第2の結晶を含むソース・ドレイン領域と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】P型FETとN型FETとを半導体基板に形成された半導体装置において、ゲート電極をフルシリサイド化して、P型FETの移動度を高め、N型FETのオン電流を増やすことを可能とする。

【解決手段】半導体基板11にN型FETとP型FETとが形成され、前記N型FETのゲート電極14NとP型FETのゲート電極14Pとがフルシリサイド化されている半導体装置1において、前記P型FETのゲート電極14Pは、ゲート長方向の断面形状が前記半導体基板11表面より上方に行くに従いゲート長が短くなる形状に形成されていて、前記N型FETのゲート電極14Nは、ゲート長方向の断面形状が前記半導体基板11表面より上方に行くに従いゲート長が長くなる形状に形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SiO2よりも高い誘電率を有する材料からなる絶縁膜上に設けられた金属電極の仕事関数が所望の値を有する半導体装置を提供することを可能にする。

【解決手段】半導体基板34と、半導体基板上に形成されたトンネル絶縁層36と、トンネル絶縁層上に設けられた浮遊ゲート電極37と、浮遊ゲート電極上に形成され高誘電率材料からなる第1絶縁層38aと、この第1絶縁層上に形成されシリコンおよび酸素ならびに窒素を含むかあるいはシリコンおよび窒素を含む第2絶縁層38bとを有する電極間絶縁膜38と、電極間絶縁膜上に形成された制御ゲート電極40と、第2絶縁層と制御ゲート電極との界面に形成され13族元素を含む界面層44と、制御ゲート電極の両側の半導体基板に形成されたソース・ドレイン領域35と、を含み、界面層の前記13族元素の結合状態数は酸化、窒化、または酸窒化結合状態の総数よりも金属結合状態の数が多い。

(もっと読む)

半導体装置

【課題】半導体装置のインパクト・イオン化を利用して導通させる場合の電圧を低下し、しかも良好なスイッチング特性を有する半導体装置を提供する。

【解決手段】ソース101、ドレイン102、ソース101、ドレイン102間に設けられたI領域I、I領域I上にゲート酸化膜104を介して設けられるゲート電極105と備えたSiを基板とする半導体装置において、I領域Iに、少なくともゲルマニウムを含むエピタキシャル成長層103を選択的エピタキシャル成長によって形成する。

(もっと読む)

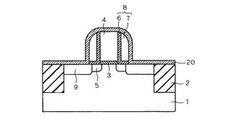

半導体装置およびその製造方法

【課題】駆動能力を向上させた半導体装置を提供する。

【解決手段】半導体装置には、ゲート幅方向に断続的に深さの変化する凹部を設けるためのトレンチ部3が形成されており、ゲート絶縁膜6を介して、トレンチ部3の内部及び上面部にゲート電極7が形成されている。ゲート電極7のゲート長方向の一方の側にはソース領域9が形成されており、他方の側にはドレイン領域10が形成されている。ソース領域9とドレイン領域10の少なくとも一部では、ゲート電極7の形成前にトレンチ部3の内壁からイオン注入を用いて不純物添加をおこなった後、拡散および活性化の熱処理を施すことによって、トレンチ部3の表面から底部にかけて深く形成させることを可能とする。これにより、ゲート電極7の凹部上面に集中して流れていた電流がトレンチ部3の全体に一様に流れるようになり、ゲート幅方向に深さが変化するように形成された凹部の実効的なゲート幅が広がる。このため、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

161 - 180 / 445

[ Back to top ]