Fターム[5F140BG32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644) | イオン注入 (445)

Fターム[5F140BG32]に分類される特許

81 - 100 / 445

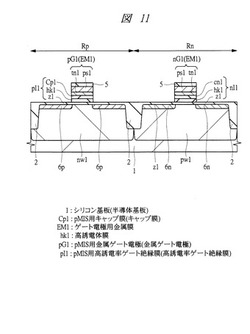

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率材料を含むゲート絶縁膜と、高融点金属等を含むゲート電極とを備え、消費電力の低減と高速動作化とが図られた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、高誘電率膜を含む絶縁膜101aを形成する工程(a)と、上面に酸化膜が形成され、高融点金属または高融点金属の化合物の少なくとも一方を含む第1の導電膜102aを形成する工程(b)と、酸化膜103aを間に挟んで第1の導電膜102a上に、シリコンを含む第2の導電膜104aを形成する工程(c)と、第1の導電膜102aおよび第2の導電膜104aに対してイオン注入を行い、酸化膜103aの構成材料を前記第2の導電膜104a中のシリコンと混合させてミキシング層103bを形成する工程(d)と、熱処理を行ってミキシング層103bを導電層103cにする工程(e)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体素子

【課題】構造が複雑なフィールドプレート構造を用いずに、ゲート電極端での電界集中を緩和することができる半導体素子を提供する。

【解決手段】MOSFET10は、基板上にバッファ層を介して形成されたp−GaN層14と、ゲート絶縁膜15と、ゲート電極20と、ソース電極と、ドレイン電極17とを有する。ゲート電極20は、ゲート電圧を印加するための電極で、ドーパントが高濃度にドーピングされたポリシリコンを用いた第1の領域(ゲート電極1)21と、高抵抗のポリシリコンを用いた第2の領域(ゲート電極2)22とを有する。両ゲート電極21、22間に抵抗勾配部23がある。第2の領域22では緩やかに電位が変化する電位勾配30ができる。これにより、ゲート電極端31において、電圧の微分である電界がピーク32で示すように小さくなり、ゲート電極端31での電界集中を緩和することができる。

(もっと読む)

デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法

【課題】デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法を提供する。

【解決手段】デュアルゲート不純物ドーピング方法は、第1領域及び第2領域を有する半導体基板上のゲート導電膜に第1導電型の不純物イオンをドープする段階であって、ゲート導電膜の下部よりも上部における不純物ドーピング濃度がより高い濃度勾配でドープする段階と、第2領域のゲート導電膜をオープンさせるマスクを用いて第2領域のゲート導電膜に第2導電型の不純物イオンをドープする段階と、熱処理を行い、第1導電型及び第2導電型の不純物イオンを拡散させる段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETを含む半導体装置において、プロセスフロー及び工程数を増やさずに、短チャネル効果を抑制した高耐圧MOSFETを製造する。

【解決手段】閾値電圧制御のために、チャネル形成領域に不純物のイオン注入をするとき、チャネル形成領域に、不純物導入する領域と不純物導入されない領域を設ける。上記不純物導入されない領域をうまくパターニングすることによって、ウェル領域とソース領域、及び、ウェル領域とドレイン領域それぞれの、境界近傍のチャネル形成領域における、ウェル領域と同じ導電型の不純物濃度を濃くし、逆短チャネル効果を誘起させることができる。上記の手段で誘起させた逆短チャネル効果と、短チャネル効果とを相殺させることによって、高耐圧MOSFETの短チャネル効果を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法と、それを実現する半導体装置の製造装置とを提供する。

【解決手段】半導体装置の製造方法は、半導体層を有する基板上または基板上に形成された導電膜上に、貴金属を含む合金膜を形成する工程(a)と、基板に対して熱処理を行って貴金属とシリコンとを反応させ、基板上または導電膜上に貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応記合金膜を除去する工程(c)と、基板を酸化性雰囲気に曝すことによって、貴金属の残渣の下に位置する部分を含むシリサイド膜の上面上にシリコン酸化膜を形成する工程(d)と、第2の薬液を用いて貴金属の残渣を溶解する工程(e)とを備えている。

(もっと読む)

81 - 100 / 445

[ Back to top ]