Fターム[5F140BG32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644) | イオン注入 (445)

Fターム[5F140BG32]に分類される特許

121 - 140 / 445

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】

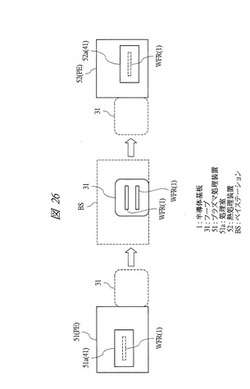

半導体基板1の主面にゲート絶縁膜用の絶縁膜を形成する。それから、プラズマ処理装置51の処理室51a内で、半導体基板1の主面のゲート絶縁膜用の絶縁膜をプラズマ窒化する。その後、プラズマ処理装置51から半導体基板1をフープ31内に移送し、フープ31をベイステーションBSに移動させてそこで待機させて半導体基板1を保管する。ベイステーションBSに待機している間、半導体基板1を保管しているフープ31内に、フープ31に設けられた第1の呼吸口から窒素ガスを供給し、フープ31に設けられた第2の呼吸口からフープ31内の窒素ガスを排出する。その後、フープ31を熱処理装置52に移動させて、半導体基板1を熱処理装置52の処理室内に搬入して熱処理する。

(もっと読む)

半導体装置及びその製造方法

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

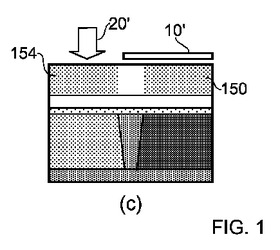

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧を要求されるMOSトランジスタおよびその製造方法を提供する。

【解決手段】LOCOS酸化膜を用いたオフセットMOSトランジスタにおいて、高耐圧が要求されるドレイン拡散層周辺のLOCOS酸化膜をエッチングし、LOCOS酸化膜が薄くなった領域の下方の半導体基板表面領域にまでドレイン拡散層を形成することによって、ドレイン拡散層端部がオフセット拡散層によってカバーされるため、ドレイン拡散層下部の領域で発生する電界集中を緩和することができ、50V以上の電圧下においても安全に動作しうるMOSトランジスタとなる。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、p型不純物を、異なる注入エネルギーでn型半導体層内部と表面に多段注入し、熱処理により同時に拡散してp型ウェル領域とする。これにより、表面からある程度の深さ(5μm程度)までの不純物プロファイルが略平坦なp型ウェル領域を得ることができ、その表面に形成されるチャネル層の特性変動も抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイドの異常成長によるリーク電流の増大を低減した半導体装置を実現できるようにする。

【解決手段】半導体装置は、ゲート電極22Aの側面上に第1サイドウォール23Aと第2サイドウォール24Aとが形成されている。半導体基板10におけるゲート電極22Aの側方には第1高濃度不純物領域31Aが形成されている。第1高濃度不純物領域31Aの外側方で且つ第1高濃度不純物領域よりも深い位置には、第2高濃度不純物領域32Aが形成されている。第2サイドウォール23Aよりも外側で且つ第2高濃度不純物領域32Aよりも深い位置には、第1高濃度不純物領域31A及び第2高濃度不純物領域32Aよりも不純物濃度が低い、低濃度不純物領域33Aが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度の向上を実現し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10に形成されたチャネル領域44上にゲート絶縁膜18を介して形成されたゲート電極20bと、ゲート電極の側壁部分に形成されたサイドウォール絶縁膜26と、ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層38と、ソース/ドレイン拡散層に埋め込まれ、半導体基板と格子定数が異なる半導体層52とを有し、半導体層は、半導体基板のうちのサイドウォール絶縁膜の下方領域に食い込むように形成された第1の突出部54と、半導体基板のうちのサイドウォール絶縁膜の直下の部分に食い込むように形成された第2の突出部56とを有している。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体素子及びその製造方法

【課題】素子分離領域と活性領域との界面に隣接した活性領域のエッジ部分に生じる寄生トランジスタによって、ゲート電圧Vgによるドレイン電流Idの応答で好ましくないハンプ現象の発生を回避することができる半導体素子半導体素子及びその製造方法を提供する。

【解決手段】基板に絶縁領域である素子分離領域により規定され、前記素子分離領域との界面に隣接したエッジ部分と、該エッジ部分により取り囲まれるセンター部分とを含む活性領域と、前記活性領域及び前記素子分離領域上に形成され、前記活性領域のセンター部分と重畳するセンターゲート部分と、前記活性領域のエッジ部分と重畳するエッジゲート部分と、前記センターゲート部分のみに形成される第1導電型の第1不純物ドーピング領域とを含むゲート電極と、前記活性領域と前記ゲート電極との間に介在配置されるゲート絶縁膜とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜上にポリシリコン膜3を形成する工程と、前記ポリシリコン膜の下層側に重元素の不純物イオン4をイオン注入する工程と、前記ポリシリコン膜の上層側に、前記重元素より質量の小さい軽元素の不純物イオン6をイオン注入する工程と、前記ポリシリコン膜を加工することにより、前記ゲート絶縁膜上にゲート電極3aを形成する工程と、前記半導体基板に不純物イオンをイオン注入し、熱処理を施すことによりソース・ドレイン領域の拡散層9を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】生産性を損なうことなく、MISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1の主面s1のNMIS領域RNには素子用pウェルpwを、PMIS領域RPには素子用nウェルnwを形成した後、主面s1に順に形成したゲート絶縁膜GIおよび第1多結晶シリコン膜E1aを透過させるようにしてアクセプタとなる不純物イオンを注入して、チャネル領域CHの不純物濃度を調整する。その後、第1多結晶シリコン膜E1aおよびその上に形成した第2多結晶シリコン膜のうち、NMIS領域RNにはドナー不純物を、PMIS領域RPにはアクセプタ不純物を注入した後、これらを加工して、n型のゲート電極とp型のゲート電極とを形成する。ゲート絶縁膜GIは、シリコン基板1の主面を酸化した後、炉体内において一酸化二窒素雰囲気中で熱処理を施すようにして形成する。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】十分に低いリーク電流、高い電気的ストレス耐性、及び高いエッチング耐性を有する絶縁膜を半導体基板の表面に堆積する、半導体装置の製造方法、並びに、その絶縁膜を備える半導体装置を提供する。

【解決手段】シリコンソースと酸化剤とを交互に供給して半導体基板の表面にシリコン酸化膜を堆積する、半導体装置の製造方法であって、前記シリコンソースの供給を、前記半導体基板へ前記シリコンソースの分子が吸着飽和することなく吸着量が増加する供給条件で行い、前記酸化剤の供給を、前記半導体基板に吸着された前記シリコンソースの分子中に不純物が残存する供給条件で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

横型半導体装置

【課題】 バイポーラで動作する横型半導体装置において、オン電圧を低くする技術を提供する。

【解決手段】 半導体装置10は、半導体層54の表面に設けられている第1主電極20と第2主電極2を備えている。半導体層54は、第1主電極20に接触しているn型の第1半導体領域24と、第2主電極2に接触しているp型の第2半導体領域58と、第1半導体領域24と第2半導体領域58の間に設けられているn型の第3半導体領域12を有している。第3半導体領域12は、第1半導体領域24と第2半導体領域58を結ぶ第1方向に沿って伸びている第1層8と第2層40を有している。第1層8と第2層40は、第1方向に直交する第2方向に並んでいる。第1層8は、不純物濃度が第1方向に均一である。第2層40は、第1層8よりも不純物濃度が濃く、不純物濃度が第1半導体領域24側から第2半導体領域58側に向けて増加している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】側面方位とキャリア極性に応じて歪み方向が最適化されたFinFETおよびナノワイヤトランジスタと、これを実現するSMTを導入した製造方法を提供する。

【解決手段】半導体基板14と、半導体基板14の上部に形成され、半導体基板14主面に平行な上面と、半導体基板14主面に垂直な(100)面の側面を有する直方体状半導体層40と、直方体状半導体層40内に形成されるチャネル領域18と、チャネル領域18の少なくとも側面上に形成されるゲート絶縁膜20と、ゲート絶縁膜20上のゲート電極30と、直方体状半導体層40内に、チャネル領域18を挟み込むよう形成されるソース/ドレイン領域とを備え、チャネル領域18に、半導体基板14主面に対して垂直方向の圧縮歪みが印加されているpMISFETを有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧を要求されるMOSトランジスタを含む半導体装置およびその製造方法を提供する。

【解決手段】LOCOSオフセットMOSトランジスタにおいて、LOCOS酸化膜の一部をエッチングした領域にドレイン拡散層を形成することにより、オフセット拡散層によってドレイン拡散層下部の電界集中が発生する領域がカバーされた50V以上の電圧下においても保証しうる高耐圧MOSトランジスタを含む半導体装置を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板上方に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜とシリコンを含むゲート電極との間に、炭素を含むキャップ層を設ける。

(もっと読む)

121 - 140 / 445

[ Back to top ]