Fターム[5F140BG32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644) | イオン注入 (445)

Fターム[5F140BG32]に分類される特許

41 - 60 / 445

半導体装置の製造方法

【課題】 トランジスタの深さ方向の濃度プロファイルが均一化され、閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

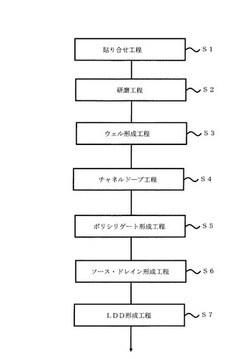

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOS型トランジスタは、第1導電型の第1シリコン基板と、第1シリコン基板に対して積層された第2導電型の第2シリコン基板と、ウェル領域と、ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるMOS型トランジスタであって、第1シリコン基板と第2シリコン基板とを貼り合せる工程と、第2シリコン基板をチャネル領域の深さまで研磨する工程と、第2シリコン基板に対して不純物イオン注入することによりソース・ドレイン領域を形成する工程と、チャネル領域上にゲート電極を形成する工程と、を含む。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】全反応方式のサリサイドプロセスを用いず、部分反応方式のサリサイドプロセスによりゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の熱処理では、ランプまたはレーザを用いたアニール装置ではなく、カーボンヒータを用いた熱伝導型アニール装置を用いて半導体ウエハを熱処理することにより、少ないサーマルバジェットで精度良く薄い金属シリサイド層41を形成し、最初の熱処理によって金属シリサイド層41内にNiSiの微結晶を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ構造を有するMOSトランジスタにおいて、チャネル領域のしきい値の適切な調整が可能となる半導体装置を提供する。

【解決手段】第1導電型半導体基板に作られたゲート幅方向に深さが変化する凹部領域と凸部領域の前記凹部領域はトレンチ構造で形成されているトレンチ構造を有するMOSトランジスタにおいて、前記第1導電型半導体基板表面に沿って成膜した犠牲酸化膜を介して形成された第1導電型ドープドポリシリコン膜を前記凹部領域のトレンチ構造に埋め込ませて熱処理をおこなうことで、前記トレンチ構造間の凸部領域上面およびトレンチ構造の凹部領域側面と底面に不純物拡散する。これにより、トレンチピッチが縮小されてもチャネルへの均一な不純物添加が可能になる。

(もっと読む)

半導体装置の製造方法

【課題】バラツキの小さな高特性、高信頼性の半導体装置の製造方法を提供する。

【解決手段】ゲート電極の側壁に窒化膜サイドウォールを形成し、ウエットエッチングにより、ソース・ドレイン形成予定領域上のゲート酸化膜を除去することにより、窒化膜サイドウォール下方にアンダーカットが入るが、ゲート電極下方にはアンダーカットは入らない。これにより、ソース・ドレインのシート抵抗ばらつき増大を抑制し、また、シリコン基板にダメージを導入してしまうこともないため、接合リーク、しきい値ばらつき等の不具合を引き起こすことがない。

(もっと読む)

半導体装置の製造方法

【課題】不純物イオン注入時に形成されたフレンケル型結晶欠陥を終端させ、ボロンの増速拡散を抑制することで、逆短チャンネル効果を改善した半導体装置の製造方法を提供する。

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOSトランジスタは、P型ウェル領域と、N型ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるNMOSトランジスタであって、N型ソース・ドレイン領域を不純物イオン注入により形成する工程と、ソース・ドレイン領域と同一領域に、ハロゲン元素をイオン注入する工程と、ソース・ドレイン領域を活性化させるための活性化熱処理工程とを含む。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の一部を高誘電体膜で構成した場合に好適な2種ゲート構造を提供する。

【解決手段】基板1上に窒化シリコン膜よりも比誘電率が大きい高誘電体膜、例えば酸化チタン膜6(内部回路のゲート絶縁膜)を堆積した後、酸化チタン膜6の上部に窒化シリコン膜7を堆積する。窒化シリコン膜7は、次の工程で基板1の表面を熱酸化する時に酸化チタン膜6が酸化されるのを防ぐ酸化防止膜として機能する。次に、内部回路領域に窒化シリコン膜7と酸化チタン膜6を残し、I/O回路領域の窒化シリコン膜7と酸化チタン膜6を除去した後、基板1を熱酸化することによって、I/O回路領域の基板1の表面に酸化シリコン膜8(I/O回のゲート絶縁膜)を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

41 - 60 / 445

[ Back to top ]