Fターム[5F140BG52]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁の形成方法及び除去 (3,620) | 堆積 (1,344) | CVD (924)

Fターム[5F140BG52]に分類される特許

121 - 140 / 924

半導体装置およびその製造方法

【課題】シリサイド層とシリコンの界面抵抗を低く保ちつつ、シリサイド層からの金属元素の拡散を抑制し、リーク電流および寄生抵抗を小さくする。

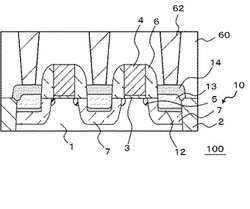

【解決手段】半導体装置100は、基板1(半導体層)と、基板1に接して形成され、基板1とは逆導電型の半導体電極10と、半導体電極10上に半導体電極10に接して形成されたシリサイド層14と、ゲッタリング層12内部において、基板1と半導体電極10との接合およびシリサイド層14からそれぞれ離れて形成され、シリサイド層14に含まれる金属元素をゲッタリングするゲッタリング層12と、を含む。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

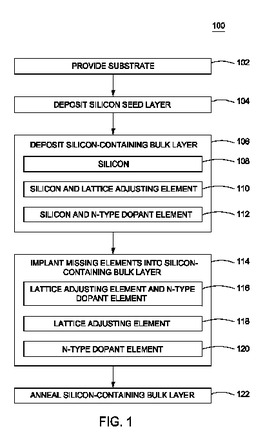

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】 DMOSトランジスタのオン抵抗のバラツキをなくすために、チャネル抵抗のバラツキが生じない製造方法を提供する。

【解決手段】 半導体基板上に第1ボディー領域を形成した後、ゲート酸化膜上にゲート電極膜を積層する。第2ボディー領域を形成するためフォトレジストをマスクとして使用し、開口を形成する。本発明は、フォトレジストを残したまま開口内に不純物イオンを注入し、チャネル領域を構成する第2ボディー領域を形成する。さらに同じマスクを使用して第1ソース領域を形成する。次に、ゲート電極を形成し、サイドスペーサーを形成した後、第2ソース領域とドレイン領域とを同時に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の下部からゲート電極の形成されていない基板上の領域に斜め方向のイオン注入を行って形成される不純物拡散領域を有する半導体装置において、半導体装置のサイズを従来に比して縮小化することができる半導体装置を提供する。

【解決手段】N型半導体層13の表面に形成されるP型のベース領域21と、ベース領域21内に形成されるP+型ソース領域22およびN+型ソース領域23を有するソース領域と、N型半導体層13の表面にベース領域21から離れて形成されるN+型のドレイン領域26と、ソース領域とドレイン領域26との間にゲート絶縁膜41を介して形成されるゲート電極42と、ドレイン領域26からゲート電極42の下部にかけて、ドレイン領域26に隣接して形成されるN型のドリフト領域と、を備え、ゲート電極42とゲート絶縁膜41との積層体のソース領域側側面の高さが、ドレイン領域側側面の高さよりも高く形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

121 - 140 / 924

[ Back to top ]