Fターム[5F140BH27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | ソース、ドレイン材料 (598)

Fターム[5F140BH27]の下位に属するFターム

多結晶 (39)

Fターム[5F140BH27]に分類される特許

141 - 160 / 559

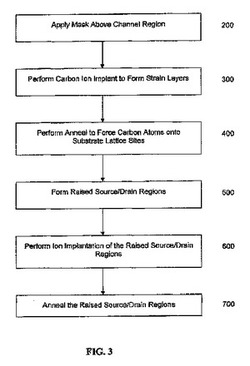

低温炭素及び/又は分子炭素注入された歪み薄膜上の隆起型ソース/ドレインの形成

半導体構造のチャネル領域に引張応力を増大する方法が開示される。この方法は、1つ以上の低温炭素又は分子炭素イオン注入ステップを実行することを含み、炭素イオンを半導体構造中に注入して、チャネル領域の両側に歪み層を生成する。次に、隆起型ソース/ドレイン領域が歪み層上に形成され、続いて隆起型ソース/ドレイン領域をドープするためにイオン注入ステップが用いられる。ミリ秒アニールステップは、歪み層及び隆起型ソース/ドレイン領域を活性化する。歪み層は半導体構造のチャネル領域中のキャリア移動度を増大させる。一方、隆起型ソース/ドレイン領域は、隆起型ソース/ドレイン領域にその後ドーパントイオンを注入することによって引き起こされる、歪み層中のひずみの低減を最小化する。 (もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル特性を低下させることなく、チャネル領域に十分な歪みを生じさせることのできる半導体層が埋め込まれたソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】N型のシリコン基板11の主面にゲート絶縁膜を介して形成されたゲート電極13と、ゲート電極13の下方に形成されるチャネル領域14を挟むように形成され、チャネル領域14に歪みを与えるためのゲルマニウム、P型不純物のボロンおよびボロンの拡散を抑制するためのカーボンを含有する第1半導体層15a、15bと、ゲルマニウムおよびボロンを含有する第2半導体層16a、16bと、が順に積層された構造を有するソース・ドレイン領域17a、17bと、第2半導体層16a、16bのゲート電極13側の側面からチャネル領域14に隣接するエクステンション領域18a、18bと、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】フィン型電界効果トランジスタの寄生抵抗を低減し、駆動電流を増大させる。

【解決手段】半導体基板本体部101と、半導体基板本体部101の上に突成された、フィン108と、を有し、フィン108は、両端側の一対のソース/ドレイン領域106および一対のソース/ドレイン領域106に挟まれたチャネル領域107を有するものとして構成された、半導体基板と、

半導体基板本体部101の上に形成された、シリコン酸化物からなる、素子分離絶縁膜102と、

素子分離絶縁膜102の上に形成された、シリコン窒化物又はシリコン炭窒化物からなる、被膜109と、

チャネル領域107におけるフィン108の上に形成されたゲート絶縁膜と、

ゲート絶縁膜を介してフィン108におけるチャネル領域107を挟むように形成された、ゲート電極103と、

ソース/ドレイン領域106を覆うと共に被膜109と隙間なく当接する、応力印加層105と、を備える。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

基板(11)上に形成されたフィン型半導体領域(13)の両側部にエクステンション領域(17)が設けられている。フィン型半導体領域(13)を跨ぐと共にエクステンション領域(17)と隣り合うようにゲート電極(15)が形成されている。ゲート電極(15)と隣り合う領域のフィン型半導体領域(13)の上部に、エクステンション領域(17)よりも高い抵抗率を有する抵抗領域(37)が形成されている。 (もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層3のシリコンとソース・ドレイン拡散層上の第1の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、素子分離絶縁膜の上の第1の金属膜の表面上に第1の金属よりも融点が高い高融点金属である第2の金属を堆積して、少なくとも第1の金属膜の表面を被覆するように第2の金属膜を形成し、第2の加熱温度の第2の加熱処理により、少なくとも第1の金属膜の表面を第2の金属膜と反応させて、合金膜106aを形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加させ、合金膜、第1の金属膜の未反応部分、および、第2の金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ、P型トランジスタともに低い閾値電圧が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板上の第1領域201にN型トランジスタが形成され、前記基板上の第2領域202にP型トランジスタが形成された半導体装置101であって、前記基板111と、シリコンを含有する第1のゲート絶縁膜121と、第1の金属と酸素とを含有する第2のゲート絶縁膜122と、前記第1の金属と異なる第2の金属と酸素とを含有する第3のゲート絶縁膜123と、ハフニウムを含有する第4のゲート絶縁膜124と、金属と窒素とを含有するゲート電極層131とを備え、前記第2領域に形成された前記ゲート電極層の厚さは、前記第1領域に形成された前記ゲート電極層の厚さよりも厚くなっている。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置

【課題】素子分離端における薄膜化を抑制しつつ、第1半導体層と格子定数の異なる第2半導体層を第1半導体層に埋め込む。

【解決手段】Ox、NまたはCの斜めイオン注入16を第1半導体からなる半導体基板11に行うことにより、半導体基板11を構成する第1半導体よりもエッチングレートが小さなエッチブロック層17を素子分離溝12の側壁に形成し、第1半導体よりも格子定数が大きな第2半導体を凹部25内にエピタキシャル成長させることにより、第2半導体からなる埋め込み層26を凹部25内に選択的に形成する。

(もっと読む)

歪誘起合金及び段階的なドーパントプロファイルを含むその場で形成されるドレイン及びソース領域

【解決手段】

トランジスタのドーパントプロファイルは、その場で(in situ)ドープされた歪誘起半導体合金に基いて得ることができ、段階的なドーパント濃度が高さ方向に沿って確立され得る。その結果、半導体合金をチャネル領域にごく近接して位置させることができ、それにより全体的な歪誘起効果を高めることができる一方で、最終的に得られるドーパントプロファイルについて過度に妥協しなくてよい。更に、半導体合金を選択的に成長させるのに先立ち追加的な注入種が組み込まれてよく、それにより内部歪の注入誘起緩和を回避することができる。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体電子デバイス

【課題】耐圧性が高く反りが小さい半導体電子デバイスを生産性高く提供すること。

【解決手段】陽極化成してSi基板の一部を多孔質化したSi層を含む基板と、前記基板上に形成された、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが、交互に積層した2層以上の複合層を有するバッファ層と、前記基板と前記バッファ層との間に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、を備えた半導体電子デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

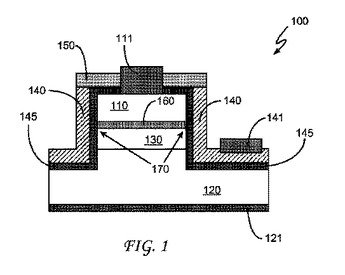

トンネル電界効果トランジスタ及びその製造方法

トンネル電界効果トランジスタ(TFET)は、ソース領域(110、210)、ドレイン領域(120、220)、ソース領域とドレイン領域との間のチャネル領域(130、230)、及びチャネル領域に隣接するゲート領域(140、240)を含む。ソース領域は、第1のIII族材料と第1のV族材料とを有する第1の化合物半導体を含み、チャネル領域は、第2のIII族材料と第2のV族材料とを有する第2の化合物半導体を含む。ドレイン領域は、第3のIII族材料と第3のV族材料とを有する第3の化合物半導体を含む。  (もっと読む)

(もっと読む)

141 - 160 / 559

[ Back to top ]