Fターム[5F140BH27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | ソース、ドレイン材料 (598)

Fターム[5F140BH27]の下位に属するFターム

多結晶 (39)

Fターム[5F140BH27]に分類される特許

161 - 180 / 559

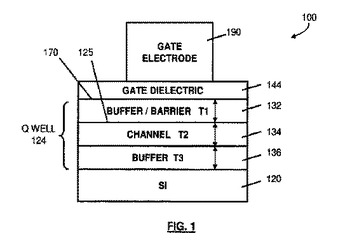

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

段階的な形状の構造を有する埋め込み歪誘起材質を伴うトランジスタ

【解決手段】

トランジスタにおいて、段階的な形状のキャビティを設けることによって、シリコン/ゲルマニウム、シリコン/炭素、等のような歪誘起半導体合金がチャネル領域に極めて近接して位置させられてよく、キャビティは次いで歪誘起半導体合金で充填されてよい。この目的で、異なるエッチング挙動の2つ以上の「使い捨て」スペーサ要素が、対応するキャビティの異なる深さで異なる横方向オフセットを規定するために用いられてよい。その結果、高い均一性及びこれに伴い低減されたトランジスタばらつきが、洗練された半導体デバイスに対してさえも達成され得る。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコン単結晶から切り出されたシリコン基板表面にシリコンエピタキシャル層が成膜堆積されたエピタキシャルウェーハであって、

前記シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3 とされてなる。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

電界効果トランジスタ

【課題】オン動作時における耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、キャリア走行層上に形成され、キャリア走行層とは反対の導電型を有し、キャリア走行層に到る深さまで形成されたリセス部によって分離したキャリア供給層と、分離した各キャリア供給層上にリセス部を挟んで形成されたソース電極およびドレイン電極と、分離した各キャリア供給層上にわたってリセス部内におけるキャリア走行層の表面を覆うように形成されたゲート絶縁膜と、リセス部においてゲート絶縁膜上に形成されたゲート電極と、を備え、ソース電極側のキャリア供給層は、該ソース電極直下に位置するソースコンタクト領域と、ゲート電極の下方に位置し、ソースコンタクト領域よりもキャリア濃度が低いソース電界緩和領域とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 素子分離絶縁膜の微細化、及びMOSトランジスタの性能向上を図る。

【解決手段】

第1のMOSトランジスタと第2のMOSトランジスタを有する半導体装置において、第1のMOSトランジスタ11が形成される半導体基板100の第1の領域10と、第1の領域10に隣接され、かつ第2のMOSトランジスタ21が形成される半導体基板100の第2の領域20と、第1領域10と第2領域20の間に形成された第1の素子分離絶縁膜30と、第1領域10に形成された複数層の半導体エピタキシャル層12とを有し、第1の素子分離絶縁膜30のアスペクト比が6.7以上である半導体装置。

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置

【課題】素子分離領域から受ける応力に基づいた、トランジスタの駆動力を低下させる歪みを緩和し、さらに、歪みシリコン技術を用いることでトランジスタの駆動力を向上させることができる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板内にソース・ドレイン領域およびチャネル領域を有するトランジスタと、ゲート幅方向から前記チャネル領域を挟むように設けられ、前記所定の結晶と異なる格子定数を有するエピタキシャル結晶が埋め込まれた拡張領域と、を備えた半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

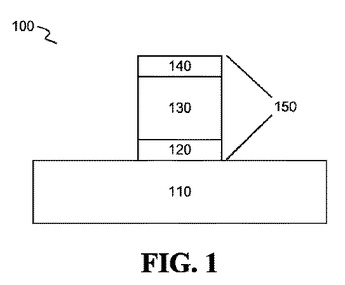

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体層に形成したリセスにモフォロジの良好な別の半導体層をエピタキシャル成長させる。

【解決手段】Si基板上にゲート絶縁膜、ゲート電極及びサイドウォールスペーサを形成した後(ステップS1,S2)、そのSi基板のソース・ドレイン領域を形成する部分に、ドライエッチングで第1リセスを形成する(ステップS3)。そして、ドライエッチングによってエッチングダメージが生じた第1リセスの表層部をウェットエッチングで除去することによって第2リセスを形成した後(ステップS4)、第2リセスにSiGe層をエピタキシャル成長させる(ステップS5,S6)。これにより、Si基板に形成したリセスに、モフォロジの良好なSiGe層を形成することが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系結晶またはGe系結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、水素ガス雰囲気中において、圧力が第1の圧力であり、温度が第1の温度である条件下で、シリコン窒化物からなる部材を備えたSi系基板の前記部材に覆われていない領域の自然酸化膜および付着したシリコン窒化物を除去する工程と、水素ガス雰囲気中において、圧力を前記第1の圧力に保持したまま、温度を前記第1の温度から第2の温度に下げる工程と、水素ガス雰囲気中において、温度を前記第2の温度に保持したまま、圧力を前記第1の圧力から第2の圧力に下げる工程と、圧力を前記第2の圧力に下げた後、水素ガス、およびSiおよびGeのうちの少なくともいずれか1つを含む前駆体ガス雰囲気中において、前記Si系基板の表面にSiおよびGeのうちの少なくともいずれか1つを含む結晶をエピタキシャル成長させる工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

161 - 180 / 559

[ Back to top ]