Fターム[5F140BJ27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444) | プラグを有するもの (1,074)

Fターム[5F140BJ27]に分類される特許

961 - 980 / 1,074

MIS型トランジスタおよびその製造方法

【課題】S/D拡散層抵抗の低減とゲート寄生容量の低減とを同時に実現することのできるMIS型トランジスタ及びその製造方法の提供。

【解決手段】MIS型トランジスタは、半導体基板と、この基板上に形成されたソース・ドレイン領域と、このソース・ドレイン領域間のチャネル領域の上方に設けられたゲート電極と、を備える。このMIS型トランジスタにおいて、前記チャネル形成面を挟んで設けられた前記ソース・ドレイン領域の上面が、前記チャネル形成面よりも嵩上げされてゲート電極側に位置し、かつ、前記ソース・ドレイン領域の上面は、嵩上げされて前記ゲート電極側に位置するレベルの実質的な平坦面と、この平坦面のレベルから前記チャネル形成面のレベルまで傾斜する傾斜面と、を備えると共に、前記チャネル形成面の上側に設けられたゲート絶縁膜により囲まれるゲート電極の形状が、段部を介して下側が先細りとなった断面T字の形状となっている。

(もっと読む)

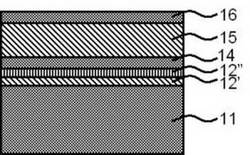

半導体基板及び半導体装置並びにそれらの製造方法

【課題】多孔質層或いは多孔質領域上に良質の半導体層を形成することを目的とする。

【解決手段】半導体基板の製造方法は、第1材料で構成される基板11上に、基板11の格子定数と異なる格子定数を有する第2材料からなる層を含む第1半導体層12を形成する工程と、少なくも第1半導体層11の表面を多孔質化して多孔質層12”を形成する工程と、多孔質層12”上に第1材料で構成される第2半導体層14を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の端部近傍領域に自己整合的にオーバーラップし、電界緩和層として働く、低濃度拡散層を有する高耐圧MOSトランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 第1のN−低濃度拡散層105と、ゲート電極端部126を画定する熱酸化膜106とは、共に、シリコン窒化膜103からなるパターンをマスクとして自己整合的に形成され、更に、第1のN−低濃度拡散層105に隣接する第2のN−低濃度拡散層109は、ゲート電極108をマスクとして自己整合的に形成される。結果、電界緩和層として働く第1のN−低濃度拡散層105と、ポリシリコンゲート電極108の端部近傍領域に位置する熱酸化膜106とは、水平方向位置でみて、互いに自己整合的にオーバーラップしている。ポリシリコンゲート電極108の端部近傍領域にオーバーラップし、電界緩和層として働く第1のN−低濃度拡散層105が、ゲート電極端部126に自己整合的に形成される。

(もっと読む)

半導体集積回路装置およびpチャネルMOSトランジスタ

【課題】 pチャネルMOSトランジスタの動作速度を向上させる。

【解決手段】 pチャネルMOSトランジスタのチャネル領域両側にSiGe混晶層をエピタキシャルに形成し、前記チャネル領域に一軸性圧縮応力を発生させる。さらにゲート電極をゲート側壁絶縁膜を介して、圧縮応力を蓄積した圧縮応力膜により覆い、前記チャネル領域に面内圧縮応力を、さらに印加する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】耐圧BVdssが確保され、さらにセット電流の経時的な変化が抑制されるとともに、増幅素子のオン抵抗が小さい電界効果トランジスタを提供する。

【解決手段】本発明に係る電界効果トランジスタは、半導体基板2上に離間して形成されたソース電極30およびドレイン電極29と、ソース電極30とドレイン電極29との間に配置されたゲート電極22と、を備え、

ゲート電極22とドレイン電極29との間の領域において、半導体基板2の上部に絶縁膜21を介してフィールドプレート電極(24,26)が設けられ、

半導体基板2の表面は平坦であり、半導体基板2とフィールドプレート電極(24,26)との距離が、ゲート電極22からドレイン電極29に向かうに従って増大するように構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】

Ge元素を用いることなく、プロセス信頼性や結晶品質が高く、応力管理が容易な、歪みSiを利用した高移動度チャネルを有する半導体装置を提供する。

【解決手段】

Si基板の表面に、300nm以下の段差dがついた絶縁膜12,14を形成し、絶縁膜14の窓あけ部から横方向に延びて該絶縁膜14を覆うように、800℃以上の高温でSi単結晶のエピタキシャル成長を行う。次に、CMP研磨により絶縁膜12をストッパとしてエピタキシャル層22を研磨し、段差dと同じ厚みに制御されたSi層を有するSOI領域を得る。該SOI領域では、Siと絶縁膜の熱膨張率差と、成膜温度及び室温との温度差により残留応力26が発生し、Siに引っ張り応力がかかって格子歪みが発生する。前記SOI領域にMOS構造を形成することで、高移動度チャネルを有する歪みSi−MOSFETが得られる。

(もっと読む)

評価用半導体デバイス、評価用半導体デバイスの作製方法、半導体デバイスの評価方法

【課題】 動作(駆動)中の半導体デバイスの動作状況を測定して、上記半導体デバイスをより正確に価できる評価用半導体デバイス、評価用半導体デバイスの作製方法、半導体デバイスの評価方法を実現する。

【解決手段】 半導体基板2上に設けられた任意の半導体デバイスの、ドレイン、ソース、ゲートの各電極3a、4a、5と、各電極3a、4a、5間に形成されたキャリアの分布状態が制御されるアクティブ領域2aとを設ける。各電極3a、4a、5上を覆う絶縁膜7を設ける。観察すべきアクティブ領域2aを露出させた露出面1aを形成する。各電極3a、4a、5を外部と接続させるために、絶縁膜7中に配線部3b、4b、5aをそれぞれ設ける。

(もっと読む)

半導体装置

【課題】 従来の半導体装置では、過電圧から素子を保護するために設けられたN型の拡散領域が狭く、ブレークダウン電流が集中し、保護用のPN接合領域が破壊されてしまうという問題があった。

【解決手段】 本発明の半導体装置では、基板2とエピタキシャル層3とに渡りN型の埋込拡散層4が形成されている。P型の埋込拡散層5が、N型の埋込拡散層4上面の広い領域に渡り形成され、過電圧保護用のPN接合領域17が形成されている。P型の拡散層6が、P型の埋込拡散層5と連結するように形成されている。PN接合領域17のブレークダウン電圧は、ソース−ドレイン間のブレークダウン電圧よりも低い。この構造により、ブレークダウン電流の集中を防止し、過電圧から半導体装置を保護することができる。

(もっと読む)

半導体装置およびその製造方法ならびに電子装置

【課題】 線型の電力増幅器において、高周波特性に影響を及ぼす帰還容量のドレイン電圧依存性を抑えて歪み特性の劣化を防ぐことができる技術を提供する。

【解決手段】 半導体基板40上にゲート絶縁膜44を介してゲート電極45を形成する。このゲート電極45のドレイン領域側の側壁を覆うようにフィールドプレート電極59aを形成する。そして、このフィールドプレート電極59aの電位をフローティング状態にする。フィールドプレート電極59aは、例えばポリシリコン膜より形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】大きなディボットやコンタクト接続不良の発生を回避しつ半導体基板にストレスをかけることにより、キャリアの移動度を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に、ゲート絶縁膜3を介してゲート電極4が形成されている。ゲート電極4の両側における半導体基板1には、ソース・ドレイン領域8が形成されている。素子分離用溝2の内壁から、ソース・ドレイン領域8上およびゲート電極4上まで連続してライナー膜11が形成されている。ひとつなぎにしたライナー膜11により、半導体基板1にストレスをかけて、キャリアの移動度を向上させる。ライナー膜11は、コンタクト13の形成のためのエッチングストッパとしての役割ももつ。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ横型パワーMOSFETにおいて、信頼性を高めること。また、デバイスピッチを小さくすること。

【解決手段】半導体基板にn型ウェル領域2、p型オフセット領域4を形成し、トレンチ5を形成する。トレンチ5の第1の側壁に沿ってゲート酸化膜13を形成し、トレンチ5の第2の側壁に沿ってフィールドプレート酸化膜14を形成し、それぞれの酸化膜の内側にゲートポリシリコン電極11およびフィールドプレート12を形成する。トレンチ5の第1の側壁に接して基板表面領域にn型ソース領域7を形成するとともに、トレンチ5の第2の側壁の外側の基板表面領域にn型ドレイン領域6を形成する。層間絶縁膜でトレンチ5の内部を埋めるとともに、n型ソース領域7およびn型ドレイン領域6の表面を覆い、その層間絶縁膜にコンタクトホールを開口する。そして、ソース電極10とドレイン電極9を形成する。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性基材42中に、当該絶縁膜の膜強度を向上させる絶縁性粒子41を含有してなるものである。この絶縁膜は、絶縁性粒子41として、絶縁性基材42の比誘電率と異なる比誘電率の粒子を用いることにより、その比誘電率を調整したものである。例えば、絶縁性粒子41として、絶縁性基材42の比誘電率より低い比誘電率の粒子を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

垂直なゲート電極のトランジスタを備える半導体装置及びその製造方法

【課題】垂直なゲート電極のトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】本発明のトランジスタ構造体は、横方向で対向する第1及び第2の側面と縦方向で対向する第3及び第4の側面を有する半導体パターンと、半導体パターンの第1及び第2の側面に隣接して配置されるゲートパターンと、半導体パターンの第3及び第4の側面に直接接触しながら配置される不純物パターンと、ゲートパターンと半導体パターンとの間に介在されるゲート絶縁膜パターンと、を備える。これにより、ゲートパターンがチャネル領域の側面に配置されるので、半導体装置の集積度を増加させることと同時にトランジスタのチャネル幅を増加させうる。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性粒子41の集合体の間隙を、当該絶縁膜の膜強度を向上させる絶縁性の充填物42で充填してなるものである。この絶縁膜は、充填物42として、絶縁性粒子41の比誘電率と異なる比誘電率の材料を用いることにより、その比誘電率を調整したものである。例えば、充填物42として、絶縁性粒子41の比誘電率より低い比誘電率の材料を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

半導体装置およびその製造方法

【課題】 コンタクトプラグとのコンタクト抵抗を低減したトランジスタを有する半導体装置を提供する。

【解決手段】 トランジスタとコンタクトプラグとを有する半導体装置であって、トランジスタのドレイン電極は、ゲート電極側に設けられ、導電性不純物が拡散された第1の不純物拡散層3と、第1の不純物拡散層よりもゲート電極から離れて配置され、コンタクトプラグと接触し、第1の不純物拡散層よりも濃度の高い第2の不純物拡散層4と、第2の不純物拡散層よりもゲート電極から離れて配置され、コンタクトプラグと接触し、第2の不純物拡散層よりも濃度の高い第3の不純物拡散層5とを有する構成である。

(もっと読む)

半導体装置

【課題】 本発明は、メモリセルトランジスタに所定の電位を転送するための転送トランジスタを小型化することができる半導体装置を提供することを目的とする。

【解決手段】 半導体基板100の表面上にゲート絶縁膜120を介して形成されたゲート電極130と、半導体基板100の表面部分において、ゲート電極130の下方に位置するチャネル領域160の両側に、ゲート電極130の形状に対応するようにそれぞれ形成されたソース領域170A及びドレイン領域170Bと、ソース領域170A又はドレイン領域170B上に形成された第1及び第2のコンタクトプラグ190A及び190Bとを備え、第1及び第2のコンタクトプラグ190A及び190Bは、第1及び第2のコンタクトプラグ190A及び190B間の距離として所定の距離LCを確保するように千鳥配置されたことを特徴とする。

(もっと読む)

半導体装置

【課題】高濃度の酸素不純物を含むシリコン基板上に形成した高耐圧MOSトランジスタを有する半導体装置を提供する。

【解決手段】p型シリコン基板1に、約3〜5μm程度の深さを有する約3×1015〜1×1016cm-3の濃度のn型不純物からなる延長ドレイン領域2及び、n型不純物からなるソース領域3を形成する。p型シリコン基板1は、CZ法によりシリコン基板の製造が行われ、また不純物であるボロンを導入し、p型の特性を得ている。このp型不純物の濃度は、1×1015cm-3である。また、p型シリコン基板1の上におけるn型延長ドレイン領域2の下方に、延長ドレイン領域2と半導体基板1との接合部から、約10〜50μmの深さに約3×1015cm-3〜1×1016cm-3の濃度と約0.5〜2μmの厚さで、n型不純物からなる埋め込み層10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 隣接するゲート電極を狭ピッチで配置できる上、埋め込みによりシリコン基板面上での微細化を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 シリコン半導体基板1上に形成された隣り合うトランジスタのゲート電極と、トランジスタ間に金属層を埋め込んでなり、各ゲート電極9,10の端部がゲート絶縁膜8を介して金属層の端面に重なるように配置された埋め込み金属層7と、各ゲート電極の他端部側に形成されたLDD領域16,17とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】

酸化シリコンより誘電率の高い高誘電率絶縁膜を有する半導体装置を提供する。

【解決手段】

半導体装置の製造方法は、(a)シリコン基板の活性領域表面にSiOまたはSiONの界面層を形成し、(b)界面層上方に酸化シリコンより高い誘電率を有するHfSiON等の高誘電率のゲート絶縁膜を形成し、(c)ゲート絶縁膜上方にポリシリコンのゲート電極を形成し、(d)高誘電率のゲート絶縁膜形成前後の少なくとも一方で、基板表面をパッシヴェーション処理し、(e)少なくともゲート電極、高誘電率のゲート絶縁膜をパターニングして絶縁ゲート電極構造を形成し、(f)絶縁ゲート電極構造両側の活性領域にソース/ドレイン領域を形成する。

(もっと読む)

プラズマダメージ層の評価方法および半導体装置の製造方法

【課題】 シリコン基板の主面上に形成された非常に軽微なダメージのプラズマダメージ層であっても検出することのできる技術を提供する。

【解決手段】 シリコン基板上に例えば酸化シリコン膜からなる層間絶縁膜を形成し(ステップS1、S2)、この層間絶縁膜にコンタクトホールを形成するためプラズマエッチングする(ステップS3)。このプラズマエッチングはシリコン基板が露出するまで行われるため、シリコン基板の主面上にはプラズマダメージ層が形成される。このシリコン基板を酸化し(ステップS4)、シリコン基板上に形成された酸化膜の膜厚を測定(ステップS5)することで、プラズマダメージ層の検出、評価を行う。

(もっと読む)

961 - 980 / 1,074

[ Back to top ]