Fターム[5F140BK34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | 熱処理 (1,281) | シリサイド化 (1,222)

Fターム[5F140BK34]の下位に属するFターム

雰囲気 (113)

Fターム[5F140BK34]に分類される特許

141 - 160 / 1,109

III族窒化物系へテロ電界効果トランジスタ

【課題】オン動作時には電子移動の抵抗が低く、かつオフ動作時にはゲート電極と2次元電子ガスとのゲートリーク電流が発生しにくいIII族窒化物系へテロ電界効果トランジスタを提供する。

【解決手段】本発明のIII族窒化物系へテロ電界効果トランジスタは、基板と、該基板の上に設けられるキャリア走行層と、該キャリア走行層上に、ヘテロ界面を形成するように設けられる障壁層と、該障壁層上の一部からキャリア走行層の内部まで掘り込まれたリセス構造と、該リセス構造上に設けられる絶縁層と、該絶縁層上に設けられるゲート電極とを含み、キャリア走行層および障壁層はいずれも、III族窒化物半導体からなり、絶縁層は、リセス構造の側面上に形成される側面絶縁層と、リセス構造の底面上に形成される底面絶縁層とからなり、側面絶縁層の厚みは、前記底面絶縁層の厚みよりも厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置の製造装置

【課題】希釈された溶液を用いて、貴金属を含む被処理膜等を迅速に且つ効果的にエッチングでき、且つ、設備の稼働率を向上できるようにする。

【解決手段】薬液を調合する薬液調合槽24と、調合された薬液を貯蔵する薬液貯蔵槽28と、貯蔵された薬液を用いて半導体基板を処理する処理チャンバ21とを有する半導体装置の製造装置を用いた半導体装置の製造方法は、薬液調合槽24において、酸化剤と錯化剤とを混合して第1の薬液を調合し、薬液調合槽24において、第1の薬液を活性化する。続いて、薬液貯蔵槽28において、活性化された第1の薬液と純水とを混合し、第1の薬液の濃度及び温度を調整することにより、第1の薬液を希釈した第2の薬液を調整する。続いて、処理チャンバ21に投入された半導体基板に第2の薬液を供給する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTを構成するバイポーラトランジスタのターンオフ時間を短くし、かつIGBTを構成するバイポーラトランジスタを動作しやすくする。

【解決手段】シンカー層115は第1導電型ウェル102及び第2導電型ドリフト層104それぞれに接しており、かつ第1導電型コレクタ層108から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とシリコンの界面抵抗を低く保ちつつ、シリサイド層からの金属元素の拡散を抑制し、リーク電流および寄生抵抗を小さくする。

【解決手段】半導体装置100は、基板1(半導体層)と、基板1に接して形成され、基板1とは逆導電型の半導体電極10と、半導体電極10上に半導体電極10に接して形成されたシリサイド層14と、ゲッタリング層12内部において、基板1と半導体電極10との接合およびシリサイド層14からそれぞれ離れて形成され、シリサイド層14に含まれる金属元素をゲッタリングするゲッタリング層12と、を含む。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】応力絶縁膜により、MISトランジスタの駆動能力が劣化することを防止する。

【解決手段】第1のMISトランジスタpTr1は、第1の活性領域10aにおける第1のサイドウォール19Aの外側方下に設けられたトレンチ22内に形成され、第1の活性領域10aにおけるチャネル領域のゲート長方向に第1の応力を生じさせるシリコン混晶層23を含む第1導電型の第1のソースドレイン領域27aと、第1の活性領域10a上に第1のゲート電極14a、第1のサイドウォール19A及び第1のソースドレイン領域27aを覆うように形成され、第1の応力とは反対の第2の応力を生じさせる応力絶縁膜31とを備えている。シリコン混晶層23の最上面は、第1のゲート電極14a直下に位置する半導体基板10の表面よりも高く形成されている。シリコン混晶層23と第1のサイドウォール19Aとの隙間24には、第1の応力緩和膜28aが形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

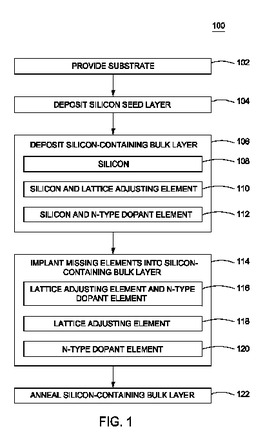

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

141 - 160 / 1,109

[ Back to top ]