Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

141 - 160 / 232

チップレス・エピタキシャルソース/ドレイン領域を有する半導体デバイス

チップエクステンション部のないチップレス・エピタキシャルソース/ドレイン領域を有する半導体デバイス、及びその製造方法が提供される。一実施形態において、当該半導体デバイスは基板上にゲートスタックを有する。該ゲートスタックは、ゲート誘電体層上にゲート電極を有し、基板内のチャネル領域上に位置する。当該半導体デバイスはまた、基板内のチャネル領域のそれぞれの側に一対のソース/ドレイン領域を有する。該一対のソース/ドレイン領域はゲート誘電体層に直に接触し、且つ該一対のソース/ドレイン領域の格子定数はチャネル領域の格子定数と異なる。一実施形態において、当該半導体デバイスは、誘電体のゲートスタックプレースホルダーを用いて形成される。  (もっと読む)

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

本発明はトランジスタに関し、このトランジスタでは、フィールドプレートを用いて、重要な区域の活性領域(チャネル)の電界を弱める(制御する)ことにより、電界が素子に渡って均等に分布する。本発明の目的は、トランジスタとその製造方法を提供することであり、これにより活性領域の電界が均される(すなわち電界ピークが低くなる)ことであり、ここで素子はより安価におよびより簡単に製造できる。本発明による半導体素子は、基板(20)であって、この上に半導体物質からなる少なくとも1つの層(24、26)を含む活性層構造が設けられた基板を備え、ここでこの活性層構造(24、26)の上にソースコンタクト(30)とドレインコンタクト(28)とが配置されており、そしてソースコンタクト(30)とドレインコンタクト(28)とは互いに離されており、そしてゲートコンタクト(32)の少なくとも一部がソースコンタクト(30)とドレインコンタクト(28)の間の活性層構造(24、26)の上に配置されており、ここでゲートフィールドプレート(34)はゲートコンタクト(32)と電気的に接続されており、そしてここで、ここで追加的に少なくとも2つの分離したフィールドプレート(50、52、54、56、58、60)が活性層構造(24、26)の上にまたは直接パッシベーション層(36)の上に配置される。  (もっと読む)

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法。

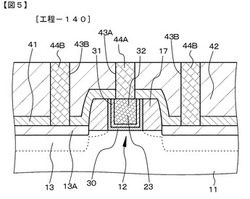

【課題】ゲート電極の上方に層間絶縁層を形成するときに、ゲート電極に対向する基体の部分が酸化されることが無い、絶縁ゲート電界効果トランジスタの製造方法を提供する。

【解決手段】絶縁ゲート電界効果トランジスタの製造方法は、(a)ソース/ドレイン領域13、チャネル形成領域12、チャネル形成領域12上に形成されたゲート絶縁膜30、ソース/ドレイン領域13を覆う絶縁層21、及び、チャネル形成領域12の上方の絶縁層21の部分に設けられたゲート電極形成用開口部22を備えた基体を準備し、(b)ゲート電極形成用開口部22内を導電材料層31,32で埋め込むことでゲート電極23を形成し、次いで、(c)絶縁層21を除去し、その後、(d)全面に、第1の層間絶縁層41、第2の層間絶縁層42を、順次、成膜する工程を備え、前記工程(d)において、酸素原子を含まない成膜雰囲気中で第1の層間絶縁層41を成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板を加熱処理した際に温度分布の発生を抑制することができる半導体装置の製造方法とその製造方法により得られる半導体装置を提供する。

【解決手段】基板11に形成された半導体素子部12を分離するための素子分離領域13からその素子分離領域に設けられた仮素子分離膜45を除去し、素子分離領域13に絶縁膜が形成されていない状態で基板11を加熱処理し、その後に半導体素子部12を覆うとともに素子分離領域13を埋める層間絶縁膜41を成膜する。これにより、基板11に形成された半導体素子部12を分離する素子分離領域13に設けられた素子分離膜34と、素子分離膜34とは異なる絶縁材料からなり、素子分離領域13において半導体素子部12に接して設けられた分離側壁32と、半導体素子部12と素子分離領域13とを覆い、素子分離膜34との間には界面が存在しない層間絶縁膜41を有する半導体装置10を得る。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド構造を有する半導体装置において、接合リーク特性を劣化させずにゲート細線抵抗を向上することができる半導体装置を得ること。

【解決手段】シリコン基板1上にゲート絶縁膜12を介して形成されたポリシリコン膜14およびシリサイド膜15からなるゲート電極13と、ゲート電極13の下部のチャネル領域を挟んで形成された所定の導電型の不純物イオンが拡散された拡散層17、および拡散層17の表面に形成されるシリサイド膜18からなるソース/ドレイン領域と、を有する半導体装置において、ゲート電極13のシリサイド膜15の膜厚が、拡散層17上のシリサイド膜18の膜厚よりも厚い。

(もっと読む)

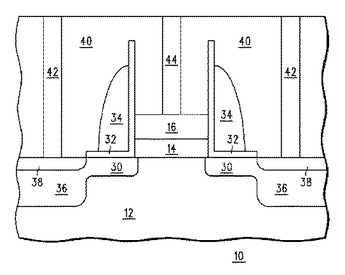

III族窒化物素子のための活性領域成形およびその製造方法

その底部孔口よりも幅が広い最上部孔口を有するゲートウェルを備えるパッシベーション体を含むIII族窒化物ヘテロ接合パワー半導体素子、およびその製造方法。  (もっと読む)

(もっと読む)

金属電極を有する半導体素子の形成、及び半導体素子の構造

半導体素子(10)を形成する方法は、ゲート誘電体(14)を基板(12)の上に形成する工程と、金属電極(16)をゲート誘電体(14)の上に形成する工程と、ポリシリコンまたは金属を含む第1犠牲層(18)を金属電極の上に形成する工程と、第1犠牲層(17)を除去する工程と、そしてゲート電極コンタクト(44)を金属電極(16)の上に位置し、かつ金属電極(16)に接続されるように形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、ゲート電極がバックゲート領域上に配線され、バックゲート領域に寄生電流が発生し、オン抵抗値が変動し易いという問題があった。

【解決手段】本発明の半導体装置では、バックゲート領域としてのP型の拡散層5と重畳するように、ソース領域としてのN型の拡散層6が形成されている。そして、N型の拡散層6と対向するように、ドレイン領域としてのN型の拡散層7が形成されている。そして、ゲート電極9は、N型の拡散層6、7が対向する領域のP型の拡散層5上を被覆するように配置されている。更に、ゲート電極9は、N型の拡散層7上に配線されている。この構造により、効率的にチャネル領域が配置され、P型の拡散層での寄生電流の発生が抑制され、Nチャネル型MOSトランジスタ1のオン抵抗値の変動が防止される。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難いゲート絶縁膜、かかるゲート絶縁膜の評価方法を提供する。

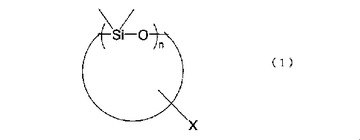

【解決手段】ゲート絶縁膜3は、下記一般式(1)で表される構造を有しており、下記一般式(1)で表される構造中のnが3または4であるものの総数をAとし、nが5以上であるものの総数をBとしたとき、{A/(A+B)}×100が1.2%以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

[式中、nは2以上の整数を表す。また、Xは水素原子または水酸基を表す。]

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の製造方法、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難く、高い絶縁破壊耐性(TZDB、TDDBの改善)が経時的に得られるゲート絶縁膜、かかるゲート絶縁膜の製造方法および評価方法、さらに、このゲート絶縁膜を用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】ゲート絶縁膜3は、半導体基板(基材)2上に化学的気相成膜法を用いて成膜され、平均厚さが10nm以下のものであり、シリコン、酸素原子および水素原子で構成され、その密度が2.5g/cm3以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

(もっと読む)

半導体装置の製造方法

【課題】長波長レーザアニールを用い半導体基板内の所定の領域を選択的にアニールする。

【解決手段】レーザ光20の照射に対し膜厚が薄くなるに従い反射率が小さくなる反射率調整膜17を、領域Anおよび領域Apを有する半導体基板1上に形成した後、領域An上の反射率調整膜17をエッチングする。次いで、半導体基板1にレーザ光20を照射し、領域Anのn−型半導体領域11、n+型半導体領域14に対して、アニールを行う。同様にして、反射率調整膜17を半導体基板1上に形成した後、領域Ap上の反射率調整膜17をエッチングする。次いで、半導体基板1にレーザ光20を照射し、領域Apのp−型半導体領域12、p+型半導体領域15に対して、アニールを行う。

(もっと読む)

半導体装置の製造方法

【課題】 素子領域のエッジコーナー部における電界集中を緩和し、トランジスタの特性劣化を防止することを可能とする。

【解決手段】半導体基板上にダミーゲート層を形成する工程と、前記ダミーゲート層の側面に、ダミーゲート層を構成する材料との間で、エッチング選択性を有する側壁絶縁膜を形成する工程と、全面に層間絶縁膜を堆積する工程と、前記層間絶縁膜を、前記ダミーゲート層の上面が露出するまで除去する工程と、前記ダミーゲート層を除去し、溝を形成する工程と、前記溝の底面にゲート絶縁膜を形成する工程と、底面にゲート絶縁膜が形成された前記溝内にゲート電極を形成する工程とを具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】金属膜と絶縁膜との反応物の生成を抑制し、良好な電気的特性を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10は、基板11と、半導体層12と、絶縁膜13と、保護膜15と、ソース電極21と、ドレイン電極22と、ゲート電極23と、を備える。半導体装置10は絶縁膜13の少なくとも上面を覆うように形成された保護膜15を備えることによって、ソース電極21とドレイン電極22とに含まれるアルミニウムと絶縁膜13とが反応することを抑制することができ、電極の抵抗増加、電流コラプスの増加を抑え、良好な電気的特性を備える。

(もっと読む)

絶縁ゲート電界効果トランジスタ

【課題】ノーマリオフ動作が可能な絶縁ゲート電界効果トランジスタを提供する。

【解決手段】このヘテロ接合電界効果トランジスタ(MISHFET)は、AlGaNバリア層104の上にソースオーミック電極105とドレインオーミック電極106が形成されている。AlGaNバリア層104上にSiNxゲート絶縁膜108、p型多結晶SiC層109、オーミック電極であるPt/Auゲート電極110が順次形成されている。p型多結晶SiC層109は仕事関数が相対的に大きいので、ゼロバイアス状態でもMISHFETのチャネルが空乏化されて、ノーマリオフ動作が生じる。

(もっと読む)

半導体装置の製造方法

【課題】処理時間が短く、かつ処理温度を高温にしなくてもトランジスタのゲート絶縁膜と半導体基板の界面に水素を十分に供給することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1の表面にトランジスタを形成する工程と、半導体基板1の表面上及びトランジスタ上に層間絶縁膜9,12及び配線層10,13を形成する工程と、最上層の配線層13上及び層間絶縁膜12上にパッシベーション膜14を形成する工程と、半導体基板1の裏面を研削又は研磨する工程と、半導体基板1の裏面から、トランジスタのゲート絶縁膜と半導体基板1の界面に水素を供給する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】導電体プラグと金属シリサイド層との接触面積を容易に確保することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板11上にゲート電極12が形成される。ゲート電極12の側面には、サイドウォール絶縁膜14が形成される。ゲート電極12およびサイドウォール絶縁膜14をマスクとして、半導体基板11に不純物領域15が形成される。不純物領域15の表面に、金属シリサイド層16が形成される。金属シリサイド層16が形成されると、サイドウォール絶縁膜14底面のエッジをゲート電極12側に後退させるエッチングが行われる。当該エッチングが行われた半導体基板11上に、ライナー膜17、および層間絶縁膜18が形成された後、層間絶縁膜18およびライナー膜17にコンタクトホール19が形成される。コンタクトホール19に導電体を充填することで、導電体プラグ20が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】STIなどの素子分離技術を用いたトランジスタにおいて、トランジスタの電流特性に優れ、かつレイアウトに起因する特性ばらつきを抑制する。

【解決手段】半導体基板1の表面部に形成されたトランジスタの活性領域2および活性領域2の周囲の素子分離領域3と、活性領域2の上部に形成されたゲート電極6と、素子分離領域3との境界において活性領域2を表面から掘り下げて形成したリセス領域4と、リセス領域4に埋め込まれた絶縁膜とを備える。

(もっと読む)

半導体装置

【課題】電子供給層と絶縁層との間の界面準位を低減させ、リーク電流やドレイン電流のコラプス等の抑制を可能とすること。

【解決手段】本発明は、基板(10)上に設けられたGaN電子走行層(12)と、電子走行層(12)上に設けられ2次元電子ガス(13)を電子走行層(12)に生成するAlGaN電子供給層(14)と、電子供給層(14)上に設けられたGaN層(20)と、GaN層(20)との間に絶縁膜(32)を介し設けられたゲート電極(34)と、を具備する半導体装置である。

(もっと読む)

高耐圧IC

【課題】高耐圧第二領域を設け、縦型パワーデバイスの高耐圧接合終端構造、集積回路ユニット間を分離する高耐圧接合終端構造、nチャネルまたはpチャネルの高耐圧横型MOSFETの高耐圧接合終端構造などとし、配線が横切っても耐圧が低下せずに高耐圧が維持でき、かつ製造コストの低い高耐圧ICを提供すること。

【解決手段】第一の出力配線61と第二の出力配線62下の電界強度を弱めるために、GDU1を取り囲む第一の高耐圧接合終端構造HVJT1と、GDU1内およびLSU内に形成される横型MOSFETを取り囲む第二の高耐圧接合終端構造HVJT2とが同一構造の高耐圧接合終端構造HVJTで構成され、かつ一体となっている。

(もっと読む)

141 - 160 / 232

[ Back to top ]