Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

101 - 120 / 232

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、MOSFETのチャネル領域に生じる歪み量を増加させ、歪みに基づく素子性能を向上させることを目的とする。

【解決手段】 本発明に係る半導体装置は、半導体基板1と、半導体基板1の上面に、第1の方向に延びて設けられた第1の絶縁膜2aと、第1の方向と垂直な第2の方向から第1の絶縁膜2aを挟んで設けられ、第1の絶縁膜2aに第2の方向の応力を与え、第1の方向の歪みを誘起させる第1の歪み誘起層3と、第1の絶縁膜2a上に設けられ、第1の絶縁膜2aからの応力を受けて第1の方向の歪みを有するチャネル領域4を含む第1の半導体層5aと、第1の方向からチャネル領域を挟んで設けられたソース領域9及びドレイン領域10と、第1の半導体層5aの第2の方向に対向する側面及び上面に設けられたゲート絶縁膜6と、ゲート絶縁膜6を介してチャネル領域4と対向して設けられたゲート電極7とを有する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】急峻な不純物分布のhalo層を備える半導体素子及び半導体素子の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体素子1は、半導体基板10と、半導体基板10に設けられる凸領域12と、凸領域12上に設けられるゲート絶縁膜100と、ゲート絶縁膜100の下の凸領域12内に位置するチャネル領域101と、凸領域12の両側に設けられ、チャネル領域101の両側にエクステンション115aを有するソースドレイン領域115と、凸領域12とソースドレイン領域115との間に設けられ、凸領域12と接触する部分に境界を有して設けられるhalo層110とを備える。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

半導体装置

【課題】メモリセルに対して設けられる選択ゲートについて、この選択ゲートのゲート長を長くすることなく、選択ゲートの制御性を向上させる。

【解決手段】本発明の一態様において、メモリセルA1に対して設けられる選択ゲートS1を含む半導体装置は、選択ゲートS1のチャネル上に形成されているゲート絶縁膜9の上面が、選択ゲートS1の素子分離領域10の上面の一部又は全部よりも高く、Tri-gate構造を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置およびその製造方法

【課題】「ひずみシリコン」技術を用いて形成された半導体装置において、NMOSトランジスタの電流駆動能力の向上を達成できるとともに、PMOSトランジスタの電流駆動能力の低下を抑制した半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板1の全面に、例えばPECVD法(プラズマ化学気相成長法)を用いて、厚さ20〜80nmのシリコン窒化膜を形成してライナー膜18とする。なお、ライナー膜18の成膜条件としては、成膜温度400℃以下で、Tensileストレスが0〜800MPaとなるように条件を設定する。そして、紫外線照射およびまたは300〜500℃の熱処理を行うことにより膜収縮させ、PMOS領域におけるライナー膜18では、ゲート電極4のサイドウォール窒化膜14の側面外方において、サイドウォール窒化膜14に沿って連続的、あるいは断続的にクラックCRを発生させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、ゲート構造の劣化を抑制した半導体装置の製造方法および半導体装置を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置の製造方法は、Si基板1上にゲート絶縁膜3およびSiN4を積層して仮ゲートパターンを形成し、Si基板1に一部が埋め込まれたソース5およびドレイン5を仮ゲートパターンを挟んで離間して形成し、ソース5、ドレイン5、およびSiN4上にSiO24を形成し、SiO24を平坦化しSiN4を除去して形成されたゲート開口部の側面にSiN8を形成し、ゲート開口部にゲート電極材料9を埋め込むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置表面に堆積された犠牲層を短時間に除去することができ、製造歩留りの向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、ゲート電極1、ドレイン電極2およびソース電極3を被覆し、半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10と、ドレイン電極2およびソース電極3の上方の第1のキャップ層7の位置に形成された複数の開口部12と、開口部12を第2のキャップ層10により封止する封止部12Aとを有し、開口部12を介して酸素プラズマを供給して犠牲層6をアッシング除去する半導体装置およびその製造方法。

(もっと読む)

半導体素子

【課題】ドナー元素を含む半導体層を備えた半導体素子を形成する場合に、このドナー元素が上層に拡散することを抑制することができる半導体素子を提供する。

【解決手段】ZnO基板上にGaドープMgZnO層、アンドープMgZnO層、窒素ドープMgZnO層、アンドープ活性層、窒素ドープMgZnO層と積層した積層体でGaの拡散を分析した。アンドープMgZnO層の次の窒素ドープMgZnO層で、拡散してきたGaの濃度が表面側になるにつれて、急激に減少しており、この窒素ドープMgZnO層の上層にGaは拡散していない。このように、ドナー元素を含む同一組成のドナー含有半導体層の一部に、アクセプタ元素を含み前記ドナー含有半導体層と同一組成のアクセプタ含有半導体層を形成することで、ドナー元素の拡散を防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の機械的強度を強め、かつ電気的な信頼性の高いウェーハレベルのパッケージングされた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板4Aと、半導体基板4A上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、電界効果トランジスタ4のドレイン電極2およびソース電極3の一方若しくは両方の上面に、内面が密着するように半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、ドレイン電極およびソース電極の一方若しくは両方の上面に接する第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10とを備える半導体装置およびその製造方法。

(もっと読む)

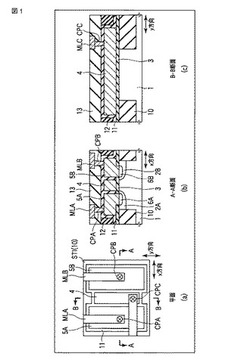

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

電界効果トランジスタ

【課題】ゲートの漏れ電流を低減させる。

【解決手段】電子トラップ及びゲート電流の漏れを減少させる窒化物系FETデバイス10である。該デバイスは、デバイスの加工に起因するトラップを減少させるため比較的厚い不動態化層20と、ゲート電流の漏れを減少させるためゲート端子38の下方の薄い不動態化層16、18とを含む。デバイスは、基板12上に堆積させた半導体デバイス層14を含む。複数の不動態化層が半導体デバイス層14上に堆積され、少なくとも2つの層はエッチストップを提供し得るよう異なる誘電性材料にて出来ている。層の間の境界面をエッチストップとして使用することにより1つ又はより多くの不動態化層18、20を除去し、ゲート端子38と半導体デバイス層14間の距離を正確に制御することができるようにし、この距離はデバイスの性能を向上させ且つゲート電流の漏れを減少させるよう極めて短くすることができる。

(もっと読む)

半導体ドライプロセス後の残渣除去液及びそれを用いた残渣除去方法

【課題】本発明は、NiSi(ニッケルシリサイド)を有する半導体デバイスの製造プロセスにおいて、ドライプロセス後の残渣を効果的に除去することが可能な残渣除去液を提供する。

【解決手段】ニッケルシリサイド(NiSi)を含む半導体基板をドライエッチング及び/又はアッシングした後に存在する残渣の除去液であって、(a)pKaが10以上のアミンのフッ化物塩、及びフッ化テトラアルキルアンモニウムを含むテトラアルキルアンモニウム塩からなる群より選ばれる少なくとも1種、(b)酸、及び(c)水を含み、該(a)の濃度が15重量%以上であり、pHが6〜9である残渣除去液に関する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、コンタクトプラグの高抵抗化を抑制することができ、また当該コンタクトプラグの構成材料のソース・ドレイン領域への拡散が起こらず、かつ簡略な製造プロセスにより作製可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ゲート電極4、第一の層間絶縁膜7、第一のコンタクトプラグ8、第二の層間絶縁膜9および第二のコンタクトプラグ10を有する。第一の層間絶縁膜7の上面は、ゲート電極4の上面と同じ高さ位置である。第一のコンタクトプラグ8は、第一の層間絶縁膜7の膜厚方向に貫通して形成され、下面においてソース・ドレイン領域5と電気的に接続され、第一の電気抵抗率を有する。第二のコンタクトプラグ10は、第二の層間絶縁膜9の膜厚方向に貫通して形成され、下面において第一のコンタクトプラグ8の上面と電気的に接続され、第一の電気抵抗率より低い第二の電気抵抗率を有する。

(もっと読む)

半導体素子の製造方法

【課題】垂直型トランジスタの形成時に、ビットライントレンチの形成工程をを単純化することができる半導体素子及びその製造方法を提供する。

【解決手段】垂直型トランジスタの形成のため、ソース/ドレーン領域に用いられる第1垂直型ピラー120と、チャンネルに用いられる第3垂直型ピラー125と、第1ビットラインインプラント領域140と、第3垂直型ピラー125の側壁を取り囲むサラウンドゲート130とで垂直型トランジスタ150を形成した後、ビットライントレンチの形成のためギャップフィル特性に優れたSOC(Spin On Carbon)膜160を形成する。SOC膜160は低温処理が可能であり、垂直型トランジスタ150に加えるストレスを最小化して倒れ問題を防止することができ、高温アニーリング工程で発生する表面の粗化現象がないので、CMP工程を省略することができる。

(もっと読む)

ストレッサ層を有するデュアル仕事関数デバイスおよびその製造方法

【課題】高誘電率ゲート誘電体を有するMOSFETトランジスタの製造方法の提供。

【解決手段】デュアル仕事関数半導体デバイスの製造方法であって、第1領域と第2領域とを有する基板を提供する工程と、第1領域と第2領域とを覆うようにゲート誘電体2を形成する工程と、該ゲート誘電体2を覆うように金属ゲート層3を形成する工程であって、歪を導入することにより変調可能な(堆積したままの)第1仕事関数を有する金属ゲート層3を形成する工程と、第1領域の上の金属ゲート層3の(堆積したままの)第1仕事関数に、第1の予め決められた仕事関数シフト(ΔWF1)を導入するように第1歪を選択し、第1領域の上の金属ゲート層3を覆うように第1歪導電層4を選択的に形成して、第1歪導電層が金属ゲート層に選択された第1歪を働かせる工程とを含む方法を提供する。この方法により得られるデュアル仕事関数半導体デバイスも記載される。

(もっと読む)

少なくとも1つの誘電体層を形成するための方法およびシステム

【課題】エッチングされた所望のアスペクト比の提供。

【解決手段】構造を形成するための方法が、基板の表面にわたって少なくとも1つの特徴部を形成するステップを含む。少なくとも1つの特徴部の上には窒素含有誘電体層を形成する。少なくとも1つの特徴部の少なくとも1つの側壁上の窒素含有層の第1の部分を、第1の速度で取り除き、少なくとも1つの特徴部の底部領域に隣接する基板の上の窒素含有層の第2の部分を、第2の速度で取り除く。第1の速度は第2の速度よりも大きい。窒素含有誘電体層の上に誘電体層を形成する。

(もっと読む)

101 - 120 / 232

[ Back to top ]