Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

81 - 100 / 232

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

熱処理方法、半導体装置の製造方法、及びフラッシュランプアニール装置

【課題】 熱処理方法、半導体装置の製造方法、及びフラッシュランプアニール装置に関し、紫外線照射による絶縁膜/半導体界面における水素で終端されたダングリング・ボンドからの水素の乖離を抑制する。

【解決手段】 加熱源となるXeフラッシュランプの放出光を、前記放出光の内の紫外線の少なくとも一部を除去した状態で酸素を含む絶縁膜とSiを含む半導体基体との界面を有する試料に照射して熱処理を行う。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ100は、基板101と、基板の上に形成されたp型GaN系半導体材料からなるチャネル層104と、チャネル層上に形成され、チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体材料からなる電子供給層106と、電子供給層の一部が除去されて表出したチャネル層104の表面に形成されたゲート絶縁膜111と、ゲート絶縁膜上に形成されたゲート電極112と、ゲート電極を挟んで形成されたソース電極109及びドレイン電極110と、電子供給層106上に形成されたゲート絶縁膜111とは別の絶縁膜であって、電流コラプス低減効果のある第2の絶縁膜113と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、しきい値電圧の低いNチャネルMISトランジスタを有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、NチャネルMISトランジスタの製造方法であって、基板に形成されたP型半導体領域上に、シリコン酸化膜とこのシリコン酸化膜上の金属酸化膜とを含むゲート絶縁膜を形成する工程と、基板を熱処理した状態で、水素ラジカルを含むガスにゲート絶縁膜を暴露する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、を具備することを特徴とする。

(もっと読む)

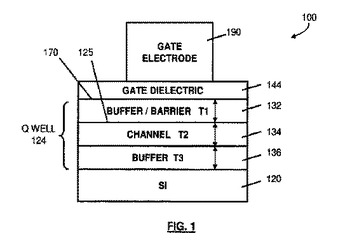

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

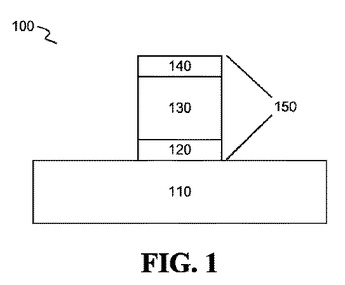

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

電界効果トランジスタの不動態化のための方法

【課題】少なくとも1つのソース電極と、ドレイン電極と、ゲート電極とを有する電界効果トランジスタの不動態化において、従来技術の問題点を解決する。

【解決手段】少なくとも1つの化学的感受性の電極を有する半導体構成素子の不動態化のために、少なくとも、該化学的感受性の電極を、ガラス層もしくはガラスセラミック層の施与によって覆い隠す。

(もっと読む)

半導体装置及びその製造方法

【課題】静止耐圧の向上と低オン抵抗化とを両立できる半導体装置及びその製造方法を提供する。

【解決手段】P型の半導体基板111内に下から順にN- 型の第1ドレインオフセット領域112、N- 型の第2ドレインオフセット領域113、及びN- 型の第3ドレインオフセット領域114が形成されている。第2及び第3ドレインオフセット領域113及び114内にP- 型のボディ領域115が形成されている。第2ドレインオフセット領域113の不純物濃度は、第1及び第3ドレインオフセット領域112及び114よりも低い。ボディ領域115のカーバチャー部131は第2ドレインオフセット領域113内に位置する。

(もっと読む)

チャネル領域への減少させられたオフセットを有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

非長方形形状を有していてよいキャビティに基いて歪誘起半導体合金を形成することができ、二酸化シリコン材質のような適切な保護層を設けることによって、非長方形形状は対応する高温処理の間にも維持され得る。その結果、歪誘起半導体材質の横方向のオフセットを小さくすることができる一方、キャビティエッチングプロセスの間に対応するオフセットスペーサの十分な厚みをもたらすことができるので、ゲート電極完全性を維持することができる。例えば、pチャネルトランジスタは六角形形状を伴うシリコン/ゲルマニウム合金を有することができ、それにより全体的な歪転移効率を顕著に高めることができる。

(もっと読む)

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡単な構成で、耐圧を保持しつつ小型化を図ることができる半導体装置を提供する。

【解決手段】ドレイン側拡散層112”Aにおけるチャネル領域116側の側面の少なくとも一部を除いた全面が、酸化膜107により、覆われている。酸化膜107は、拡散層112”Aとシリコン基板101との間の短絡を防止する。このため、酸化膜107の厚みを薄くしても、耐圧を確保できるので、装置の小型化を図ることができる。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】簡易な手順で、位置あわせ精度の高い横型電界効果トランジスタを含む半導体装置を得る。

【解決手段】高耐圧トランジスタ128は、チャネル領域170上に形成されたゲート電極110と、チャネル領域170の両側方にそれぞれ形成された第1導電型のソース領域116aおよびドレイン領域116bと、ソース領域116aとドレイン領域116bとの間に設けられ、ゲート電極110のゲート幅方向に沿って、第1導電型の不純物拡散領域と第2導電型の不純物拡散領域とがそれぞれ一定幅で交互に配置された超接合構造のドリフト領域172と、を含む。ゲート電極110は、平面視で、ドリフト領域172の第2導電型の不純物拡散領域上を覆う櫛歯を有する櫛形構造に形成された構成を有する。

(もっと読む)

半導体デバイス

【課題】エンハンスメントモードトランジスタを作製する方法を提供する。

【解決手段】基板1上の第1活性層3と、第1活性層3の上に、該第1活性層3に比較して高いバンドギャップを有する第2活性層4配設し、実質的にGaを含まないで少なくともAlを含む第2活性層4と、第2活性層4の少なくとも一部の上のゲート絶縁層5であって、第2活性層4の少なくとも一部を熱酸化して形成されたゲート絶縁層5と、ゲート絶縁層5の少なくとも一部の上のゲート電極6と、第2活性層4の上のソース電極7およびドレイン電極8とを含み、前記半導体デバイス10は、更に、動作時でゲート電極6とソース電極7が同電圧の場合、第1活性層3と第2活性層4の間で、ゲート電極6の外側でゲート電極6の位置以外に、2次元電子ガス2DEG層を含む。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のチャージアップによるMOSFETの閾値電圧Vtシフトの防止を図ることである。

【解決手段】キャパシタ下部電極3をゲート電極6aと結線し、またキャパシタ上部電極6bをP型接地層12と結線する事により、ゲート電極6aとゲート絶縁膜4から成るゲートに並列にキャパシタを形成する。この場合、キャパシタ絶縁膜5をゲート絶縁膜4に比べ薄く形成する事によりゲート電極6a上にチャージアップした電荷を、キャパシタを経由してP型接地層12に放電させる。

(もっと読む)

81 - 100 / 232

[ Back to top ]