Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

121 - 140 / 232

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置は、n型領域を有するシリコン基板と、前記n型領域上に、窒素を含む酸化シリコンを用いて形成されたゲート絶縁膜と、ホウ素を含むシリコンを用いて、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極両側の前記シリコン基板内に形成されたp型ソース/ドレイン領域と、酸化シリコンを用いて、前記ゲート電極の側壁上に形成されたサイドウォールスペーサと、前記ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜と、前記層間絶縁膜の平坦化された表面から内部に向って形成された配線用凹部と、前記凹部を埋める、下地のバリア層とその上の銅領域を含む銅配線と、前記銅配線を覆って、前記層間絶縁膜上に形成された炭化シリコン層と、を有する。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置は、n型領域を有するシリコン基板と、前記n型領域上に、窒素を含む酸化シリコンを用いて形成されたゲート絶縁膜と、ホウ素を含むシリコンを用いて、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極両側の前記シリコン基板内に形成されたp型ソース/ドレイン領域と、酸化シリコンを用いて、前記ゲート電極の側壁上に形成されたサイドウォールスペーサと、前記ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜と、前記層間絶縁膜の平坦化された表面から内部に向って形成された配線用凹部と、前記凹部を埋める、下地のバリア層とその上の銅領域を含む銅配線と、前記銅配線を覆って、前記層間絶縁膜上に形成された炭化シリコン層と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】いかなる位置に形成されたトランジスタに対してもダミーパターンを形成することを可能にして、トランジスタ特性の変動を抑制することを可能にする。

【解決手段】半導体基板11のアクティブ領域12上にゲート絶縁膜14を介して形成された複数のゲート電極15と、前記アクティブ領域12上の少なくとも前記ゲート電極15間の一部に形成されたダミーパターン16とを有し、前記ゲート電極15同士が隣接するゲート電極15−1、15−2間の間隔、および前記ダミーパターン16−1とそれと隣接する前記ゲート電極15−2、15−3との間隔が所定の範囲内となるように前記ダミーパターン16−1が形成されていることを特徴とする。

(もっと読む)

半導体素子の接合領域形成方法

【課題】 本発明は、半導体基板に接合領域を形成するにおいて、イオン注入工程を行って不純物を注入した後、活性化段階である熱処理工程を第1の熱処理工程及び第2の熱処理工程で行うが、第1の熱処理工程は、N2ガス雰囲気で行い、第2の熱処理工程は、NH3ガス雰囲気で行うことにより、後続工程を行っても接合領域の不純物が流出される現象を防止することができる半導体素子の接合領域形成方法を提供する。

【解決手段】 接合領域を含むトランジスタが形成された半導体基板が提供される段階と、接合領域を含む半導体基板の上部に保護膜を形成する第1の熱処理工程を行う段階と、保護膜を含む半導体基板上に層間絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体デバイスにおいてゲート電極高を調整するための方法

高エネルギー注入プロセス(203)中に、高度な半導体デバイス(200)のゲート電極構造(252)上に注入ブロック材料(258)を設けることによって、トランジスタ(250A,250B)のチャネル領域(255)に対する必要な遮蔽効果を得ることができる。後の製造段階において、層間絶縁材料(210)の堆積時のプロセス条件を向上させるために、注入ブロック部分(258)が除去されてゲート電極高さ(253H)が所望の高さに低減され、これにより、高密度のデバイス領域であっても、層間絶縁材料(210)内にボイドなどの不規則性が形成されるリスクを大幅に低減することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 化学機械研磨を行うことなく、比較的低コストでフルシリサイドゲート電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体基板の表面上に第1の膜(27)及び第2の膜(28)を形成する。第2の膜をパターニングすることにより、内部に開口(41c)または凹部(41d)が配置された第1のパターン(41a)と、一方向に長い第2のパターン(31a)とを形成する。第1及び第2のパターンを覆い、それらのパターンの上面上の部分の膜厚が、半導体基板の表面上の部分の膜厚よりも薄くなるように、半導体基板の上に塗布法により、第3の膜(51)を形成する。第3の膜をエッチバックすることにより、第1及び第2のパターンの上面を露出させる。全面に第4の膜(55)を形成する。第1及び第2のパターンと、第4の膜とを反応させることにより、第1及び第2のパターンを、その底面まで、金属シリサイド化物にする。

(もっと読む)

半導体デバイスのコンタクト層スタックにおいて高応力エッチストップ材料と層間絶縁膜を逐次的に提供することによる応力伝達

高い固有応力レベルの2層以上の個々の誘電層(230,330A,233,333,234,334)を、中間層間絶縁材料(250A,350A,250B,350B)と共に形成することによって、プラズマ化学気相成長法などの個々の堆積技術の制限が考慮される一方で、高度に微細化された半導体デバイス(200,300)の場合であっても、トランジスタ素子(220,320A)の上に多くの応力材料を設けることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート−ドレイン間容量を小さくしてスイッチング特性を向上できる半導体装置を提供する。

【解決手段】トレンチ6、7側壁に形成したゲート電極10とトレンチ6、7内のドレインプラグ15間に、低誘電率層間絶縁膜であるLow−k膜12を形成することで、ゲート−ドレイン間容量を低減してスイッチング特性を向上させることができる。Low−k膜12はSiOC膜、又はNCS膜である。Si基板と直接接触する部分に酸化膜などの絶縁膜を被覆し、その上にLow−k膜を形成することで、信頼性とスイッチング特性の改善を両立させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離絶縁膜を有する半導体基板とのコンタクト形成において、基板とのリークの防止する半導体装置の製造方法を提供する。

【解決手段】シリコン基板にシリコン窒化膜からなる分離窒化膜15を形成し、ウエル2、3を形成する。ゲート電極6と拡散層8、高融点金属シリサイド層9を形成し、この上に層間絶縁膜10を堆積する。層間絶縁膜をシリコン窒化膜に対するエッチング選択比の高い条件でエッチングし、コンタクトホール11を形成する。このとき、ホール下部の分離窒化膜の削れ部の深さが拡散層より浅くなるように制御する。この後、バリアメタル層28とアルミ電極14を堆積する。

(もっと読む)

半導体装置およびその製造方法

【課題】SiO2よりも高い誘電率を有する材料からなる絶縁膜上に設けられた金属電極の仕事関数が所望の値を有する半導体装置を提供することを可能にする。

【解決手段】半導体基板34と、半導体基板上に形成されたトンネル絶縁層36と、トンネル絶縁層上に設けられた浮遊ゲート電極37と、浮遊ゲート電極上に形成され高誘電率材料からなる第1絶縁層38aと、この第1絶縁層上に形成されシリコンおよび酸素ならびに窒素を含むかあるいはシリコンおよび窒素を含む第2絶縁層38bとを有する電極間絶縁膜38と、電極間絶縁膜上に形成された制御ゲート電極40と、第2絶縁層と制御ゲート電極との界面に形成され13族元素を含む界面層44と、制御ゲート電極の両側の半導体基板に形成されたソース・ドレイン領域35と、を含み、界面層の前記13族元素の結合状態数は酸化、窒化、または酸窒化結合状態の総数よりも金属結合状態の数が多い。

(もっと読む)

MIS型半導体装置の製造方法

【課題】MIS型トランジスタの短チャネル効果の抑制および、ゲートのフリンジング容量を小さくして、信号遅延の高速化を可能とすることにある。

【解決手段】MIS型トランジスタに対して、高い誘電率を有する絶縁膜でサイドウォールスペーサを形成し、これを導入端として不純物拡散層領域を形成する。高誘電率のサイドウォールスペーサの側壁は高駆動電流を達成するために必要な最適膜厚(5から15nm)とし、その外側のサイドウォールスペーサは誘電率の小さい絶縁膜(シリコン酸化膜)で構成する。

【効果】短チャネル効果を十分に抑制し、かつソース・ドレイン寄生抵抗の抑制が達成される。さらに、寄生容量を低く抑えることができるため、高い駆動能力を同時に達成することができる。

(もっと読む)

調光検知MOSFETトランジスタならびにその製造方法

【課題】光センサならびに調光装置の機能を達成し、スペースを減少させる部品構造を形成する。

【解決手段】調光検知MOSFETトランジスタであって、第一方向に沿って伸張するチャネル130により分離された2のソースおよびドレイン領域を有し、光の照射を受ける基板100と、第一方向と実質的に垂直な第二方向に沿って伸張するゲート導電性の梁(gate conductive beam)140であり、かかる梁は、少なくとも一の支持領域上で、その2つの端部のそれぞれにおいて固定され、チャネル領域130の上に位置し、当該ゲート梁は、ゲート電圧とバルク電圧間の差であって、当該梁を曲げてチャネルの表面に近づけさせるものにより制御されるその湾曲に基づいて、チャネル130に達する光にプログレッシブ変調を実行するよう、ほぼ不透明で柔軟であるゲート導電性の梁を備える。

(もっと読む)

半導体装置

【課題】上層配線と下層配線との間の絶縁耐圧を一定以上に維持しつつ、それ以外の部分の層間絶縁膜の膜厚を小さくすることができる、半導体装置を提供する。

【解決手段】半導体基板1上には、ソース配線10が形成されている。ソース配線10上には、第2層間絶縁膜12および第3層間絶縁膜14が積層されている。第3層間絶縁膜14上には、ドレイン配線15が形成されている。ドレイン配線15は、平面視でソース配線10と交差し、少なくともこの交差部分が第3層間絶縁膜14から浮いた状態で離間している。第3層間絶縁膜14とドレイン配線15との間には、隙間16が生じている。この隙間16には、低誘電率体17が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

半導体装置

【課題】上層配線と下層配線との間の絶縁耐圧を一定以上に維持しつつ、層間絶縁膜の膜厚を小さくすることができる、半導体装置を提供する。

【解決手段】下層配線としてのソース配線10上には、第2層間絶縁膜および第3層間絶縁膜が積層されている。第3層間絶縁膜上には、上層配線としてのドレイン配線15が形成されている。このドレイン配線15は、平面視でソース配線10と交差する。また、ソース配線10とドレイン配線15との間には、平面視でソース配線10とドレイン配線15とが交差する部分を含む領域24に、各層間絶縁膜の材料よりも高い絶縁性を有する材料からなる高絶縁体17が備えられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】膜組成が良好に制御されたFUSIゲート電極を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】上部にストッパ層7を積層させたシリコン電極5を半導体基板1上にパターン形成する。ストッパ層7およびシリコン電極5の側壁をサイドウォール9およびライナー膜15で覆う。ストッパ層7、シリコン電極5、サイドウォール9、およびライナー膜15を、層間絶縁膜17で埋め込み、ストッパ層7を露出させるように層間絶縁膜17の平坦化処理を行う。ストッパ層7を除去することによりシリコン電極5の表面を露出させる。シリコン電極5の表面を露出させた状態で、先の工程で露出したシリコン電極5の側壁を絶縁膜21で覆う。絶縁膜21で側壁が覆われたシリコン電極5を表面側からシリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタなどのnチャネル領域を有する電界効果トランジスタの電流駆動能力をより向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置のNMOSトランジスタ3は、nチャネル領域を有する半導体基板1と、n型ソース/ドレイン領域4と、ゲート絶縁膜7と、ゲート電極8とを含んでいる。n型ソース/ドレイン領域4は、半導体基板1上にnチャネル領域を挟むように形成されている。ゲート絶縁膜7はnチャネル領域上に形成されている。半導体装置の製造方法は、半導体基板1上にゲート絶縁膜7およびゲート電極8が形成される工程と、半導体基板1上にゲート電極8を覆うように窒化シリコンを含む薄膜20が形成される工程と、この薄膜20に紫外線が照射される工程とを有する。

(もっと読む)

半導体デバイスのデュアルストレスライナ上方の付加層を使用することによって向上するNチャネルトランジスタのトランジスタパフォーマンス

それぞれ固有応力が異なる誘電ライナ(230、240)をパターニングした後に、窒化シリコンなどの付加的誘電材料(260)を形成することによって、Pチャネルトランジスタ(220B)のパフォーマンスを実質的に低下させずにNチャネルトランジスタ(220A)のパフォーマンスを著しく向上させることができる。  (もっと読む)

(もっと読む)

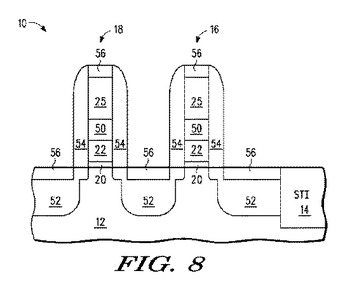

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置

【課題】従来と異なる方法によりチャネル領域に歪みを発生させたMISFET構造を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成された第1のソース・ドレイン領域および第1のチャネル領域を有するn型MISFETと、前記半導体基板上に形成された第2のソース・ドレイン領域および第2のチャネル領域を有するp型MISFETと、前記第1のソース・ドレイン領域に接続され、前記第1のチャネル領域に伸張歪みを与える第1のコンタクトプラグと、前記第2のソース・ドレイン領域に接続され、前記第2のチャネル領域に圧縮歪みを与える第2のコンタクトプラグと、を有する。

(もっと読む)

121 - 140 / 232

[ Back to top ]