Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

41 - 60 / 232

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】 トンネル絶縁膜を有するトランジスタにおいて、トンネル絶縁膜の電子トラップが増加することによるトランジスタの電気特性の劣化を抑制することが可能な半導体装置及びその製造方法を提供する

【解決手段】 実施形態に係る半導体装置は、半導体基板1と、前記半導体基板1上に形成されたトンネル絶縁膜2を含むトランジスタと、前記トランジスタの上方に形成されたBを含むシリコン窒化膜7と、を備える。前記シリコン窒化膜7は、B−N結合を有する。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

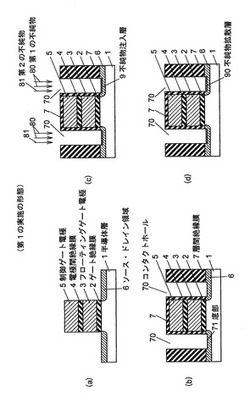

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

41 - 60 / 232

[ Back to top ]