Fターム[5F140CC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741)

Fターム[5F140CC02]の下位に属するFターム

Fターム[5F140CC02]に分類される特許

161 - 180 / 232

半導体装置の作製方法及び不揮発性半導体記憶装置の作製方法

【課題】絶縁耐圧の良好な絶縁層を製造する技術を提供することを目的とする。また、絶縁耐圧の良好な絶縁層を有する半導体装置を製造する技術を提供することを目的とする。

【解決手段】シリコンを主成分とする半導体層若しくは半導体基板に対して高密度プラズマ処理を行うことにより、半導体層の表面若しくは半導体基板の上面に絶縁層を形成する。このとき、供給ガスを希ガス、酸素及び水素を含むガスから希ガス及び酸素を含むガスに途中で切り替えて高密度プラズマ処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置、例えば、オフセットゲート構造を有するMOSトランジスタでは、デバイスサイズが縮小し難いという問題がった。

【解決手段】本発明の半導体装置、例えば、オフセットゲート構造を有するPチャネル型MOSトランジスタ1では、N型のエピタキシャル層3には、ソース領域とドレイン領域との間にLOCOS酸化膜20、21が形成されている。ゲート電極14、15は、LOCOS酸化膜20、21上に位置配置されるように形成されている。そして、ドレイン領域としてのP型の拡散層6、7及びソース領域としてのP型の拡散層12、13が、ゲート電極14、15に対して位置精度よく形成されている。この構造により、MOSトランジスタ1のデバイスサイズを縮小することができる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンを覆って設けられたゲート電極と、前記ソース領域若しくはドレイン領域から前記ゲート電極に向けて張り出し、隣接するフィンに接続して形成された張出し領域と、前記ゲート電極に接続する複数のパッド電極と、前記複数のパッド電極を接続する配線とを具備する。

(もっと読む)

高圧バイポーラCMOS−DMOS集積回路装置およびこれを形成するためのモジュール式方法

エピタキシャル層を含まない基板においてさまざまな半導体装置を製造するために全低温プロセスが用いられる。装置は分離されていないラテラルDMOS、分離されていない拡張されたドレインまたはドリフトされたMOS装置、ラテラルトレンチDMOS、分離されたラテラルDMOS、JFETおよび空乏モード装置、ならびにP−Nダイオードクランプおよびレクチファイヤおよび接合端子を含む。プロセスが高温処理の必要をなくし、「注入されたままの」ドーパントプロファイルを使用するので、残りの装置を生成するのに使用されるプロセスを変更する必要なしに、装置がICに加えられたり省略されたりすることを可能にするモジュール式アーキテクチャを構成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 高温で長時間の活性化熱処理を行うことなく、パターンエッジ部周辺に発生す

る応力を軽減することにより高濃度不純物領域の活性化熱処理で発生する転位の拡張を抑

制する。

【解決手段】 LDD構造を有するMOSトランジスタのソース・ドレイン領域の形成に

おいて、P型シリコン基板101上にゲート絶縁膜102を介して、ゲート電極103を

形成後、ゲート電極103等をイオン注入マスクとして、イオン注入を行い、さらに熱処

理によって、n−低濃度不純物領域106を形成する。さらにゲート電極に隣接するゲー

ト電極側壁104を形成する。このゲート電極側壁104等をイオン注入マスクとして、

n+高濃度不純物領域107をイオン注入で形成し、ソース・ドレイン領域108を形成

する。

さらに第1のゲート電極側壁104に隣接して、SiN膜109を形成する。その後、

ソース・ドレイン領域108の活性化熱処理を行う。

(もっと読む)

自己整合した耐熱性コンタクトを備える半導体デバイス及びその作製方法

半導体デバイスを形成する方法が、半導体基板上に半導体層を形成することによって提供される。マスクが、半導体層上に形成される。半導体層上に複数のイオン注入領域を形成するために、第1の伝導型を有するイオンがマスクによって半導体層中へ注入される。マスクによってイオン注入領域上に金属層が形成される。複数のイオン注入領域に注入されたイオンをそれぞれ活性化し、かつ複数のイオン注入領域上にオーミックコンタクトを設けるために、複数のイオン注入領域および金属層が単一工程でアニールされる。関連するデバイスも提供される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】応力の制御性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板の主表面上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極を挟むように前記半導体基板中に隔離して設けられたソースおよびドレインとを備えた絶縁ゲート型電界効果トランジスタP1と、前記ソース上に設けられた第1コンタクト配線26と、前記ドレイン上に設けられた第2コンタクト配線27と、前記ゲート電極上を覆うように設けられ、一端および他端が前記第1、第2コンタクト配線間に接続された圧電層22とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、電極パッドに過電圧が印加された際に、チップ内の回路素子が破壊されるという問題があった。

【解決手段】本発明の半導体装置では、N型のエピタキシャル層3は分離領域4、5により複数の素子形成領域に区画されている。素子形成領域の1つにMOSトランジスタ1が形成されている。MOSトランジスタ1の周囲には、PN接合領域34、35を有する保護素子が形成されている。PN接合領域34、35は、MOSトランジスタ1のPN接合領域32、33より接合耐圧が低い。この構造により、ソース電極用のパッドに負のESDサージが印加された際、PN接合領域34、35がブレークダウンし、MOSトランジスタ1を保護することができる。

(もっと読む)

半導体装置

【課題】ネガティブバイアス温度不安定性(NBTI)劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】シリコン基板のn型領域上11に、窒素を含む酸化シリコンを用いてゲート絶縁膜13を形成し、ホウ素を含むシリコンを用いてゲート電極14を形成する。p型ソース/ドレイン領域18を形成し、酸化シリコンを用いてサイドウォールスペーサ17を形成する。平坦化された表面を有する層間絶縁膜21、24、25を形成する。層間絶縁膜の表面に凹部を形成し,凹部をバリア層26と銅配線27で埋め、銅配線の上に、シランとアンモニアを含むソースガスを用い、ソースガスのアンモニアに対するシランの流量比を6%以下としたCVD法により拡散防止膜としての窒化シリコン層29を形成する。

(もっと読む)

窒化物半導体を用いたヘテロ構造電界効果トランジスタ

【課題】膜厚の小さい障壁層を用いながらも、高いチャネル電子濃度を得ることを可能とする、窒化物半導体を用いたヘテロ構造電界効果トランジスタを実現すること。

【解決手段】チャネル層(GaN層)4上に、順次、基本障壁層(AlXGa1−XN層)3、上層障壁層(AlYGa1−YN層)2、絶縁膜1が積層されてなる構造に、ソース電極5、ゲート電極6ドレイン電極7が設けられている、窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、X<Yであり、ゲート電極6下の絶縁膜1の膜厚は、1nm以上10nm以下であり、上層障壁層(AlYGa1−YN層)2の厚さは1nm以上5nm以下であることを特徴とする、窒化物半導体を用いたヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

半導体デバイス

【課題】絶縁膜を改質可能な半導体製造装置を提供する。

【解決手段】照射装置に、絶縁膜に対して第1の波長の光を照射する第1照射手段と、前記絶縁膜に対して第2の波長の光を照射する第2照射手段と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】低抵抗なコンタクトを歩留まり良く形成することができる半導体装置及びその製造方法を提供する。

【解決手段】ニッケルシリサイド層7が十分な膜厚を有する領域にコンタクトホール11を形成するとともに、金属シリサイド層7のエッチングを行い金属シリサイド層7に凹部を形成する。次いで、コンタクトホール11を所望のコンタクト径まで拡大する。これにより、コンタクトホールの底部を占めるシリサイド面積率を下げることなく、所望のコンタクトホール11のボトム面積を確保することができ、コンタクト抵抗上昇に起因する製造歩留まり低下を抑制することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力印加膜の膜厚の増大が容易な半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置が,半導体基板,ゲート絶縁膜,ゲート電極,ゲート側壁絶縁膜,層間絶縁膜,配線層,層間接続部,応力印加膜と,を具備する。この応力印加膜は,半導体基板と層間絶縁膜との間に配置される第1の部分と,ゲート電極と層間絶縁膜との間に配置される第2の部分と,ゲート側壁絶縁膜と層間絶縁膜との間に配置される第3の部分と,貫通孔の内面と層間接続部との間に配置される第4の部分と,を有し,かつ半導体基板に応力を印加する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力を強め、ドライブ電流を向上する。

【解決手段】シリコン基板1上にゲート電極15、25とサイドウォール16、26とを形成し、ゲート電極15、25の上面およびサイドウォール16、26の上面の一部を被覆するようにダミーゲートパターン6、7を形成し、その表面を被覆する応力制御絶縁膜8を形成する。応力制御絶縁膜8の応力がダミーゲートパターン6、7の上からかかることによって、ゲート電極15、25を高くした場合と同様に応力を強めることができる。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、n型領域を有するシリコン基板の上に、窒素を含む酸化シリコンを用いたゲート絶縁膜と、ホウ素を含むシリコンを用いたゲート電極とを形成する工程と、ゲート電極両側の前記シリコン基板内にp型ソース/ドレイン領域を形成する工程と、ゲート電極の側壁上に酸化シリコンを用いてサイドウォールスペーサを形成する工程と、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜を形成する工程と、層間絶縁膜の平坦化された表面から内部に向って凹部を形成し,該凹部内に下地のバリア層とその上の銅領域を含む銅配線とを埋め込む工程と、銅配線の上に炭化シリコン層を形成する工程と、 前記炭化シリコン層の上方に絶縁層をCVDで形成する工程と、を含むことを特徴とする。

(もっと読む)

同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体

【課題】 同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体を提供すること。

【解決方法】 半導体デバイス構造体を製造する方法は、基板(10)を準備するステップと、第1スペーサ(SP)を備える第1ゲート(G1)、第2スペーサ(SP)を備える第2ゲート(G2)、第1ゲート及び第2ゲートに隣接する、同じ導電型のそれぞれのソース(S)/ドレイン(D)領域、第1ゲートと第2ゲートとの中間に配置された分離領域(STI)、及び第1ゲート、第2ゲート、並びにそれぞれのソース及びドレイン領域の上にあるシリサイドを基板上に形成するステップと、中間構造体を製造するために第1スペーサ上に付加的なスペーサ(RSPS)を形成し、次いで、中間構造体全体の上に応力層を配置するステップと、を含む。

(もっと読む)

半導体装置

【課題】電極間の耐圧を向上できる半導体装置を提供する。

【解決手段】この半導体装置は、ショットキー電極であるゲート電極1はオーミック電極であるドレイン電極2側の第1の角3の内角θ1が90°を超えている。これにより、ゲート電極1とドレイン電極2との間の電界がゲート電極1の第1の角3に集中することを抑制できる。また、ゲート電極1の断面の多角形S1の第2の角5は内角θ2が鋭角であるが、内角θ2の2等分線の外向きの延長線L2がドレイン電極2および半導体層100と交差しないので、この第2の角5にはゲート電極1とドレイン電極2との間の電界が集中し難い。

(もっと読む)

半導体装置及びその作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置

【課題】本発明の目的は、オン抵抗(RON)が低く、オフ耐圧の高い半導体装置を提供することである。

【解決手段】ソース電極−ゲート電極間に形成される絶縁膜にしきい値電圧を低くするような歪み特性を持たせ、ドレイン電極−ゲート電極間に形成される絶縁膜7にきい値電圧を高くするような歪み特性を持たせることで、素子のオン抵抗(RON)を小さく、耐圧を高く保つ。

(もっと読む)

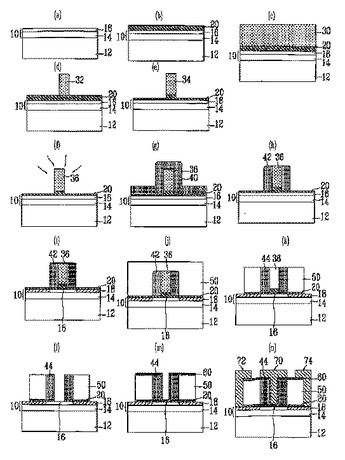

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

161 - 180 / 232

[ Back to top ]