Fターム[5F140CC12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | CVD (1,073)

Fターム[5F140CC12]の下位に属するFターム

Fターム[5F140CC12]に分類される特許

201 - 220 / 590

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

二重仕事関数半導体デバイスの製造方法及びそのデバイス

【課題】金属ゲート電極を有する二重仕事関数半導体デバイスの製造方法を提供する。

【解決手段】該製造方法は、第1領域101及び第2領域102を有する基板100を設けること、第1領域に第1半導体トランジスタ107を作製すること、第2領域に第2半導体トランジスタ108を作製すること、第1サーマルバジェットを第1半導体トランジスタに備わる少なくとも第1ゲート誘電体キャッピング層114aに作用し、第2サーマルバジェットを第2半導体トランジスタに備わる少なくとも第2ゲート誘電体キャッピング層114bに作用すること、を備える。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純AlまたはAl合金のAl系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてAl系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純AlまたはAl合金のAl系合金膜とを備えた配線構造であって、前記半導体層と前記Al系合金膜との間に、基板側から順に、窒素、炭素、およびフッ素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F)層と、AlおよびSiを含むAl−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F)層を構成する窒素、炭素、およびフッ素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

トランジスタ、半導体装置及びその製造方法

【課題】トレンチゲート型トランジスタのオン抵抗とプレーナ型トランジスタの耐圧とを同時に最適化する。

【解決手段】半導体基板10上に、半導体層16A、16Bがエピタキシャル成長により形成される。第1の領域において第1の埋め込み層12が形成され、第2の領域において第2の埋め込み層13が形成される。第1の埋め込み層12はN+型の第1の不純物層12Aと、それより広い範囲に拡散されたN型の第2の不純物層12Bとによって形成される。第2の埋め込み層13はN+型の不純物層のみで形成される。第1の領域において半導体層16Aの表面からN型の第3の不純物層18が深く拡散される。第1の領域にはトレンチゲート型トランジスタが形成され、第2の領域にはプレーナ型トランジスタが形成される。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の機械的強度を強め、かつ電気的な信頼性の高いウェーハレベルのパッケージングされた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板4Aと、半導体基板4A上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、電界効果トランジスタ4のドレイン電極2およびソース電極3の一方若しくは両方の上面に、内面が密着するように半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、ドレイン電極およびソース電極の一方若しくは両方の上面に接する第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10とを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置表面に堆積された犠牲層を短時間に除去することができ、製造歩留りの向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、ゲート電極1、ドレイン電極2およびソース電極3を被覆し、半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10と、ドレイン電極2およびソース電極3の上方の第1のキャップ層7の位置に形成された複数の開口部12と、開口部12を第2のキャップ層10により封止する封止部12Aとを有し、開口部12を介して酸素プラズマを供給して犠牲層6をアッシング除去する半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ソース領域を燐注入によって高濃度不純物のソース領域を形成すると、ソース領域表面のみ増速酸化され、ウェル領域とソース領域表面との間に段差を生じるため、チャネル抵抗が増大する。

【解決手段】炭化珪素からなる絶縁ゲート半導体装置であって、少なくともウェル領域3、ソース領域4の表面に、等しい燐の濃度プロファイルを持つ犠牲層14を形成する。このようにすれば、ゲート絶縁膜を形成するときに、ウェル領域3とソース領域4の表面で増速酸化が均一に起こり、もってウェル領域3表面とソース領域4表面の間に段差が生じることが無い。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型トランジスタ及びその製造方法において、ドレイン引き上げ用トレンチ内におけるドレイン電極の絶縁不良を抑止する。

【解決手段】半導体層14に形成された第1のトレンチ18内にトレンチゲート20を形成し、それを覆う層間絶縁膜21を形成する。その後、層間絶縁膜21、半導体層14及び埋め込み層12に延びる第2のトレンチを形成する。次に、層間絶縁膜21の開口部21Aの端に形成された突起部21Nと、第2のトレンチ22の側壁の半導体層14との段差を埋めるように、熱酸化処理によってシリコン酸化膜23を形成する。さらに第2のトレンチ内に内壁絶縁膜24を形成し、その底部の内壁絶縁膜24及びシリコン酸化膜23をエッチングして除去し、埋め込み層12を露出する。その後、第2のトレンチ22を通して埋め込み層12と接続されたドレイン電極25を形成する。

(もっと読む)

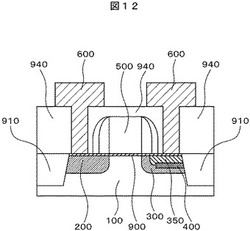

半導体装置及び半導体装置の製造方法

【課題】接触抵抗の増加が抑制されたピラー形状の縦型MOSトランジスタを用いた半導体装置を提供する

【解決手段】基部1aと複数のピラー部1Aとを有するシリコン基板1と、基部1aに設けられた一方のソースドレイン領域6と、ピラー部1Aの側面1bを覆うゲート絶縁膜4と、ゲート絶縁膜4を介してピラー部1Aの側面1bを覆うゲート電極5と、ピラー部1Aの上部に設けられた他方のソースドレイン領域12と、他方のソースドレイン領域12と接続されるコンタクトプラグ9とを備え、ピラー部1Aの上面1cの全面にコンタクトプラグ9が接続されていることを特徴とする半導体装置10。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体基板に欠陥が入るのを防止することを目的とする。

【解決手段】素子分離溝20aにより活性領域ARが画定されたシリコン基板20と、素子分離溝20a内に形成された素子分離絶縁膜23とを有し、素子分離絶縁膜23の上面が、活性領域ARにおけるシリコン基板20の上面よりも低い半導体装置による。

(もっと読む)

高ストレス薄膜の成膜方法及び半導体集積回路装置の製造方法

【課題】プロセス条件で与えられるストレス以上に大きなストレスを薄膜に与えることが可能な高ストレス薄膜の成膜方法を提供すること。

【解決手段】水素を含む成膜原料ガスをチャンバー内に供給し、水素が取り込まれた薄膜を半導体基板上に成膜する工程(ステップ1)と、薄膜から水素を離脱させる物質を含む水素離脱ガスを前記チャンバーにパルス的に供給しながら薄膜から水素を離脱させる工程(ステップ2、ステップ11及び12)と、を具備する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ゲート絶縁膜や層間絶縁膜を熱的に安定な高誘電率絶縁膜から構成し、半導体装置を製造する際の熱処理を経ても、前記高誘電率絶縁膜の、他の構成部材との反応を抑制し、前記半導体装置の特性変動を抑制する。

【解決手段】側壁をSiO2、SiN及びSiONの少なくとも一つから構成し、上部絶縁膜又はゲート絶縁膜を、希土類金属、Y、Zr、及びHfからなる群より選ばれる少なくとも一つの金属M、Al及びSiの酸化物から構成し、金属Mに対するSiの個数比Si/Mを、金属MとAlとの複合酸化物中のSiO2固溶限における比率以上であるとともに、前記上部絶縁膜又は前記ゲート絶縁膜の誘電率をAl2O3と一致する比率以下とし、金属Mに対するAlの個数比Al/Mを、Alの作用で金属Mの酸化物の結晶化を抑制する比率以上であるとともに、金属Mの作用でAl2O3の結晶化を抑制する比率以下として、半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層を設ける場所に応じて適切な特性を有するシリサイド層を備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極上に形成された第1のシリサイド層と、前記ゲート電極下方の前記半導体基板内に形成されたチャネル領域と、前記半導体基板内の前記チャネル領域を挟んだ領域に形成されるソース・ドレイン領域と、前記ソース・ドレイン領域上に形成されて前記第1のシリサイド層よりも結晶粒径の平均値が小さい、または結晶粒内の組成境界数の平均値が多い第2のシリサイド層と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、表面にp型不純物を注入したn型半導体層を順次積層し、熱処理により同時に拡散してp型ウェル領域とする。これにより、所望の耐圧を確保するのに十分な不純物濃度が所望の深さまで略均一なp型ウェル領域を得ることができる。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】窒素成分の抜けが少なく、ゲートリーク電流の増大を抑制することができるHigh−kゲート絶縁膜を成膜する、High-kゲート絶縁膜の成膜方法を提供する。

【解決手段】シリコン基板200上にHigh-kゲート絶縁膜30を形成する工程と、前記ゲート絶縁膜30を窒素及び希ガス含有ガスでHigh-kゲート絶縁膜30を窒化する工程と、前記High-kゲート絶縁膜30上に電極32を形成する工程と、前記電極32を囲むように絶縁層34を形成する工程とを有する半導体デバイスの製造方法を提供する。

(もっと読む)

201 - 220 / 590

[ Back to top ]