Fターム[5F140CC12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 製法 (1,285) | CVD (1,073)

Fターム[5F140CC12]の下位に属するFターム

Fターム[5F140CC12]に分類される特許

141 - 160 / 590

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSトランジスタのドリフト領域面におけるキャリア蓄積層が制御されるように構成された半導体装置及びその製造方法を提供すること。

【解決手段】p型基板1と、p型基板1上に形成されたn型ウェル6と、n型ウェル6に形成されたpボディ領域18と、pボディ領域18に形成されたp+型ソース領域27及びn+型ソース領域25と、n型ウェル6に形成されたn+型ドレイン領域26と、pボディ領域18とn型ウェル6との上部に形成されたゲート電極である導電性ポリシリコン層15とを備えている。ゲート電極15の直下には、厚みの異なる反転層制御用ゲート酸化膜(第1ゲート酸化膜)14と蓄積層制御用ゲート酸化膜12とを有し、膜厚が厚い蓄積層制御用ゲート酸化膜12の下面は、n型ウェル6上に、反転層制御用ゲート酸化膜14と同一面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】近年、半導体集積回路装置の製造プロセスにおいて、窒化シリコン膜等が有する応力に起因する歪を利用したキャリア移動度向上技術が活用されている。これに伴って、ウエハの表側における複雑なデバイス構造上の窒化シリコン膜を高選択で除去するため、熱燐酸によるバッチ方式ウエット処理が必須となっている。これによって、ウエハの裏面の窒化シリコン膜も除去され、一群の歪付与工程の後のプロセスにおいては、ウエハの裏側の表面はポリ・シリコン部材ということとなる。しかし、一般的なウエハの裏面等の洗浄に使用する方法は、裏面が窒化シリコン膜等であることを前提とするものであり、その特性の異なるポリ・シリコン主体の裏面を有するウエハでは洗浄の効果が十分といえない恐れがある。

【解決手段】リソグラフィ工程の前に、FPM処理の後SPM処理を実行する2工程を含むウエハ裏面に対するウエット洗浄処理を実行する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】移動体通信装置用半導体装置(RFパワーモジュール)の電力付加効率を向上させる。

【解決手段】パワーMOSFETのゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くする。これにより、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅素子をシリコンパワーMOSFETで構成したRFパワーモジュールの小型化と電力付加効率の向上を図ることができる。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程によりアモルファス化される半導体基板表面が、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を著しく低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に緩衝膜を設けることで、高濃度不純物のイオン注入を行っても、この領域の半導体基板表面がアモルファス化することを防ぐことができる。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられるNiPtSi電極の熱安定性を向上させる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、この半導体基板中のチャネル領域と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域の両側に形成され、NiおよびPtを主成分とする金属半導体化合物層からなるソース/ドレイン電極とを備え、金属半導体化合物層と半導体基板との界面において、金属半導体化合物層の単一の結晶粒と半導体基板との境界部の最大Pt濃度が、界面の平均Pt濃度よりも高いことを特徴とする半導体装置および半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

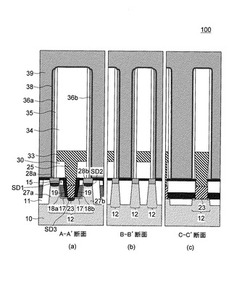

半導体装置および半導体装置の製造方法

【課題】簡易な手順で、位置あわせ精度の高い横型電界効果トランジスタを含む半導体装置を得る。

【解決手段】半導体装置100は、ゲート電極110上に、ゲート長方向の少なくとも一方側に櫛歯を有する櫛形の櫛形絶縁膜150を形成する工程と、櫛形絶縁膜150をマスクとして、半導体基板101に第1導電型の不純物イオンを注入してゲート電極110のゲート幅方向に沿って、第1導電型の不純物拡散領域と第2導電型の不純物拡散領域とがそれぞれ一定幅で交互に配置された超接合構造のドリフト領域172を形成する工程と、櫛形絶縁膜150の両側方に形成され、櫛形絶縁膜150の櫛歯の間の領域を埋め込むサイドウォール152を形成する工程と、サイドウォール152をマスクとして、ソース領域116aおよびドレイン領域116bを形成する工程と、を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に埋め込まれる絶縁膜に効率良く応力を残留させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に形成した溝内に絶縁膜を埋め込む工程と、埋め込まれた前記絶縁膜上を覆うように被覆膜を形成する工程と、前記被覆膜を形成した後、熱処理により、前記半導体基板の前記絶縁膜周辺の領域に歪みを発生させる応力を前記絶縁膜に残留させ、素子分離領域を形成する工程と、を含む。

(もっと読む)

141 - 160 / 590

[ Back to top ]