Fターム[5F140CD09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | その他の領域、その他の素子構造及び製造 (630) | フィールドプレート(内部電界の緩和以外) (252) | 内部電界の緩和 (186)

Fターム[5F140CD09]に分類される特許

61 - 80 / 186

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体装置

【課題】飽和動作時のゲート電圧が高電圧であっても素子が破壊しにくい高耐圧MOSトランジスタを提供する。

【解決手段】Nチャネル型の高耐圧MOSトランジスタの低濃度不純物領域上のLOCOSプロセスなどで形成される酸化膜と、ドレイン領域となる高濃度不純物領域との境界部の上をドレイン領域と接続している金属配線で覆うことで、境界部の低濃度不純物領域と高濃度不純物領域の接続部の電界集中を、金属配線から半導体基板に向かう電界で緩和させることができ、NMOSトランジスタの飽和動作の高ゲート電圧時の衝突電離を抑制し、素子破壊の抑制と高耐圧化を図ることが可能となる。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

電気的にプログラムされたソース/ドレイン直列抵抗を有するMOSトランジスタ

【課題】高速度MOSFETを形成するための半導体デバイス技術が要請されている。

【解決手段】トランジスタゲートサイドウォールスペーサ(27)に埋め込まれた導電層(24)を形成することによって高速MOSトランジスタ(32)は、用意される。この埋め込まれた導電層(24)は、トランジスタ(32)のゲート電極(18)とソース/ドレイン領域(28)から電気的に絶縁している。埋め込まれた導電層(24)は、ソース/ドレイン伸長領域(30)を覆うように配置され、ソース/ドレイン領域(28)直列抵抗を低くすることでソース/ドレイン伸長領域内に電荷を蓄積する。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

半導体装置

【課題】ゲート・ドレイン間容量、ゲート・ソース間容量を低減し、微細プロセスに混載しやすい電界効果トランジスタの半導体装置を提供する。

【解決手段】基板10に設けられたPウエル11と、Pウエル11に設けられたN+ソース13と、N+ドレイン12と、Pウエル11とN+ドレイン12の間に設けられた低濃度N型領域40と、領域40に設けられた絶縁層17と、N+ソース領域13と領域40との間に挟まれたPウエル11上にゲート絶縁層を介して設けられた制御電極と、制御電極と離隔して、絶縁層17上に設けられた補助電極18と、N+ソース13と接続された第1の主電極31と、N+ドレイン12と接続された第2の主電極32と、を備え、主電極31,32間で流れる主電流の方向を第1の方向と規定し、第1の方向と垂直な方向を第2の方向と規定した場合、絶縁層17の第2の方向に沿った幅が、主電極32に向かって細くなっている。

(もっと読む)

半導体装置

【課題】半導体装置内の電界集中を緩和し、高耐圧化を図る。

【解決手段】n-層110の一側にはMOSFETのチャネル領域となるpウェル111が、他側にはn+ドレイン領域118が形成される。n-層110の上方には、第1絶縁膜LAを介して複数の第1フローティングフィールドプレートFAが形成される。その上には第2絶縁膜LBを介して、複数の第2フローティングフィールドプレートFBが形成される。個々の第1フローティングフィールドプレートFAの幅と、個々の第1フローティングフィールドプレート間の距離とを等しくする。

(もっと読む)

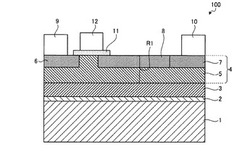

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ100は、基板101と、基板の上に形成されたp型GaN系半導体材料からなるチャネル層104と、チャネル層上に形成され、チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体材料からなる電子供給層106と、電子供給層の一部が除去されて表出したチャネル層104の表面に形成されたゲート絶縁膜111と、ゲート絶縁膜上に形成されたゲート電極112と、ゲート電極を挟んで形成されたソース電極109及びドレイン電極110と、電子供給層106上に形成されたゲート絶縁膜111とは別の絶縁膜であって、電流コラプス低減効果のある第2の絶縁膜113と、を備える。

(もっと読む)

半導体装置

【課題】半導体基板において回路が形成される領域の占有面積を削減して小型化が図られる半導体装置を提供する。

【解決手段】高電位が印加されるセンス抵抗9と第1ロジック回路26が形成された高電位ロジック領域25の周囲を取り囲むように、分離領域30を介在させて、RESURF領域24が形成されている。RESURF領域24の外側には、接地電位に対して第2ロジック回路22を駆動させるのに必要な駆動電圧レベルが印加される第2ロジック回路領域が形成されている。RESURF領域24では、電界効果トランジスタTのドレイン電極12が内周に沿って形成され、ソース電極10が外周に沿って形成されている。また、センス抵抗9に接続されたポリシリコン抵抗4が、内周側から外周側に向かってスパイラル状に形成されている。

(もっと読む)

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧FETを提供する。

【解決手段】P−型基板に形成されたN−ウエル内にP−型埋設層領域を設け、これをN−ウエル領域に形成された第1のP−型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP−型ドレイン拡散領域にも接続し、ソース電極に接続されるP−型ソース拡散領域でゲート領域の他端を定めるようにする。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

半導体装置

【課題】第1不純物領域−第2不純物領域間(たとえば、ソース−ドレイン間)の電位分布を均一にすることができる半導体装置を提供すること。

【解決手段】半導体装置1のLDMOSFET6において、エピタキシャル層3の表面におけるドレイン領域11とボディ領域7との間の部分に、ボディ領域7と間隔を空けてフィールド絶縁膜12を形成する。フィールド絶縁膜12上に、フローティングプレート17を、V1/D1=V2/D2を満たすように配置するとともに、各フローティングプレート17をそれぞれ一定電位に保持する。上記定義値は、V1:ドレインコンタクトプラグ23とフローティングプレート17との電位差、D1:ドレインコンタクトプラグ23とフローティングプレート17との間隔、V2:ゲート電極14とフローティングプレート17との電位差、D2:ゲート電極14とフローティングプレート17との間隔とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 フィールド酸化膜の厚さによらず、第1不純物領域−第2不純物領域間(たとえば、ソース−ドレイン間)における電位分布の偏りを抑制することのできる半導体装置およびその製造方法を提供すること。

【解決手段】 半導体装置1におけるLDMOSFET6において、エピタキシャル層3の表面におけるドレイン領域11とボディ領域7との間の部分に、ボディ領域7と間隔を空けてフィールド酸化膜12を形成する。そして、フィールド酸化膜12に、ドレイン領域11およびゲート電極14と間隔を空けて形成されたフローティングプレート17を埋設する。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース−ドレイン方向に垂直な方向における耐圧低下を防止し、過電圧、過電流に対する耐性も増大させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】P型半導体基板201と、N型拡散領域202と、N型拡散領域202内に形成されたP型ボディー領域206と、N型拡散領域202内に形成されたP型埋込み拡散領域204と、P型ボディー領域206内に形成されたN型ソース領域208及びP型ボディーコンタクト領域209と、N型拡散領域202内に形成されたN型ドリフト領域207と、N型ドリフト領域207内に形成されたN型ドレイン領域210と、P型ボディー領域206上に形成されたゲート絶縁膜とその上に形成されたゲート電極211と、を備え、ソース−ドレイン方向に垂直な断面において、P型埋込み拡散領域204が、ゲート電極211よりもP型ボディー領域206から離れた位置にまで延在される。

(もっと読む)

半導体装置

【課題】ノーマリーオフ動作を実現でき且つ低オン抵抗な絶縁ゲート構造の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1の窒化物半導体を含む第1の半導体層1と、第1の半導体層1上に設けられ第1の窒化物半導体よりもバンドギャップが広い第2の窒化物半導体を含む第2の半導体層2と、第2の半導体層2に接続された第1の主電極3と、第2の半導体層2に接続された第2の主電極4と、第1の主電極3と第2の主電極4との間の第2の半導体層2表面に接して設けられたフローティング電極5と、フローティング電極5上に設けられたゲート絶縁膜7と、ゲート絶縁膜7上に設けられた制御電極8と、フローティング電極5と第1の主電極3との間およびフローティング電極5と第2の主電極4との間の第2の半導体層2表面上に設けられたフィールド絶縁膜6とを備えた。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体装置

【課題】スイッチング素子において、製造ばらつきに対して所望のサステイン耐量を確保できる半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板100上に形成された第2導電型の第1拡散領域101と、第1拡散領域101上に形成された第2拡散領域108と、半導体基板100上で第2拡散領域108から所定の間隔離れた第2導電型の第3拡散領域103と、半導体基板100上に、第3拡散領域103に隣接し且つ第3拡散領域103と電気的に接続された第1導電型の第4拡散領域106と、第1拡散領域101と第3拡散領域103との間の部分上に、絶縁膜104及びその上のゲート電極105とを備える。第1拡散領域101の不純物濃度は、第2拡散領域108に電圧を印加した際に、第1拡散領域101と半導体基板100との接合面から拡張する空乏層が第1拡散領域101の主たる部分全般に形成される濃度より高い濃度である。

(もっと読む)

61 - 80 / 186

[ Back to top ]