Fターム[5F140CD09]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | その他の領域、その他の素子構造及び製造 (630) | フィールドプレート(内部電界の緩和以外) (252) | 内部電界の緩和 (186)

Fターム[5F140CD09]に分類される特許

161 - 180 / 186

III族窒化物一体化ショットキおよび電力素子

【課題】III族窒化物ヘテロ接合半導体素子を電源回路に使用したときの破壊を防止する電源回路を提供する。

【解決手段】ブースト変換回路などの電源回路で用いられるIII族窒化物ヘテロ接合半導体素子は、オーミック接合ソース・ドレイン電極と、前記ソース・ドレイン電極間のゲート電極および、前記ソース・ドレイン電極の近傍に電源スイッチと一体化されたショットキ接合電極を備える。前記ショットキ接合にはフィールドプレート電極が設けられる。

(もっと読む)

半導体装置

【課題】 LOCOSオフセット構造を採らなくても、トランジスタの耐圧が高い半導体装置の提供を提供する。

【解決手段】 MOSトランジスタ100のゲート電極11とドレインプラグ17との間のシリコン基板1上に、絶縁膜7を介して電界集中緩和用のスポットプラグ19が設けられており、このスポットプラグ19は、ゲート電極21の上方まで延ばされたソース電極21に接続している。このような構成であれば、ゲート電極11下とドレイン領域5との境界部分は、スポットプラグの影響を受けて電界集中が緩和され、その勾配が緩やかになる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ドレイン電流を低下させることなくドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】 半導体装置100は、半導体層(2)上に設けられたゲート電極(3)と、ゲート電極(3)を挟むように半導体層(2)上に設けられたソース電極(5)およびドレイン電極(9)と、半導体層(2)上のゲート電極(3)とドレイン電極(9)との間に設けられた電極(10)とを備え、電極(10)の半導体層(2)側の先端部におけるゲート・ドレイン電極間方向の幅は、10nm以上300nm以下であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 オフ状態で空乏化するドリフト領域の構造を改良することにより、高耐圧で、オン抵抗の低減した半導体装置を提供する。

【解決手段】 ドレイン・ドリフト領域190は、短冊状のn型分割ドリフト経路域1と短冊状のp型仕切領域2とが平面上で交互に繰り返し配列されたストライプ状並行構造となっている。複数のn型分割ドリフト経路域1の一方端はp型のチャネル拡散領域7にpn接合し、それらの他端はn+型のドレイン領域9に接続しており、n+型のドレイン領域9側から分岐して並列接続のドリフト経路群100を形成している。n型分割ドリフト経路域1とp型仕切領域2との幅が1μm以下になると劇的な低オン抵抗化が可能である。

(もっと読む)

半導体装置及びその製造方法並びにゲート電極構造体

【課題】 ゲート電極にオーバーラップした低濃度拡散層からなる電界緩和層を有する高耐圧MOSトランジスタ及びその製造方法を提供すること。

【解決手段】 ゲート電極106は、チャネル領域上に延在する面状部分106−4を含む第1領域と、ストライプ形状部分106−1、106−2、106−3からなるスリット群107を含む第2領域とを有する。ゲート電極106を不純物イオンの注入マスクとして、半導体基板1中に、スリット群107に対応して自己整合する複数の不純物注入領域を形成する。熱拡散処理で一体化した不純物拡散領域109を形成する。ここで、電界緩和領域は、一体化した不純物拡散領域109に含まれ、且つ、ゲート電極106の第2領域の下方に延在する。この電界緩和領域は、スリット 群107を構成するスリットの数を調整することで、ゲート電極106と、界緩和領域とのオーバーラップ寸法Ldを調整する。

(もっと読む)

半導体素子

【課題】 高い耐圧を維持しつつオン抵抗を低減化することができる半導体素子を提供する。

【解決手段】 GaNチャネル層1上にAlGaNバリア層2が形成され、この上にソース電極3、ドレイン電極4が形成され、この2つの電極に挟まれた位置に、バリア層2とショットキー接合を形成するゲート電極5が形成されている。ゲート電極2は、長手部分と短手部分が周期的に現れる櫛型形状を有する。

(もっと読む)

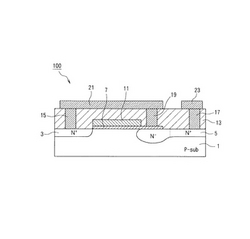

半導体装置

【課題】第1の負性抵抗領域が無い、高サージ耐量の半導体装置を提供すること。

【解決手段】p半導体基板1の表面にnウェル領域2を形成し、nウェル領域2の表面層にpウェル領域3を形成し、pウェル領域3の表面層からnウェル領域2の表面層に渡ってnオフセット領域9を形成し、このnオフセット領域9の表面層にnドレイン領域8を形成する。pウェル領域3のnドレイン領域8側は横方向拡散によりnドレイン領域8側に向かって不純物濃度が低くなるため、nドレイン領域8側に向かって不純物濃度か高くなる第2のnオフセット領域15が形成され、その結果、nオフセット領域9は不純物濃度が一定で低い第1のnオフセット領域9aと、nドレイン領域8側に向かって不純物濃度が高くなる第2のnオフセット領域15で構成される。この第2のオフセット領域の長さMをnドレイン領域8の縦方向の拡散深さNより大きくする。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】耐圧BVdssが確保され、さらにセット電流の経時的な変化が抑制されるとともに、増幅素子のオン抵抗が小さい電界効果トランジスタを提供する。

【解決手段】本発明に係る電界効果トランジスタは、半導体基板2上に離間して形成されたソース電極30およびドレイン電極29と、ソース電極30とドレイン電極29との間に配置されたゲート電極22と、を備え、

ゲート電極22とドレイン電極29との間の領域において、半導体基板2の上部に絶縁膜21を介してフィールドプレート電極(24,26)が設けられ、

半導体基板2の表面は平坦であり、半導体基板2とフィールドプレート電極(24,26)との距離が、ゲート電極22からドレイン電極29に向かうに従って増大するように構成されている。

(もっと読む)

高耐圧型半導体装置

【課題】高耐圧型半導体装置の構造の改良を図ることにより“OFF”状態において高耐圧であり、かつ、“ON”状態において低抵抗な高耐圧型半導体装置を提供する。

【解決手段】ドレイン領域16の内部にn型の不純物拡散領域15が形成され、さらに、ドレイン電極12は、n型の不純物拡散領域15に接続されている。これにより、ドレイン領域16に達したホール電流はn型の不純物拡散領域15に注入される。その結果、このn型の不純物拡散領域15からドレイン領域を通ってn-エピタキシャル層2へ電子電流が流れ出す。したがって、ソース電極11とドレイン電極12との間でホール電流と電子電流が同時に流れる形で高耐圧型半導体装置が“ON”状態となるために、“ON”状態における抵抗を大幅に削減することが可能となる。

(もっと読む)

高耐圧型半導体装置

【課題】高耐圧型半導体装置の構造の改良を図ることにより“OFF”状態において高耐圧であり、かつ、“ON”状態において低抵抗な高耐圧型半導体装置を提供する。

【解決手段】n-不純物拡散領域4がソース領域3を覆うように形成されている。これにより、n-エピタキシャル層2の空乏層化を促進することができる。したがって、“OFF”状態において、高耐圧が可能な高耐圧型半導体装置を提供することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

パワー半導体素子

【解決手段】ノンドープGaNからなるチャネル層(1)と、チャネル層(1)の表面上に形成されたn型のAl0.2Ga0.8Nからなるバリア層(2)と、バリア層(2)上に選択的に形成されたp型のAl0.1Ga0.9Nからなる半導体層(3)と、半導体層(3)の両側のうちの一方側に位置するバリア層(2)上に形成されたドレイン電極(4)と、少なくとも半導体層(3)とドレイン電極(4)との間で半導体層(3)に隣接する位置のバリア層(2)上に形成された絶縁膜(7)と、絶縁膜(7)上に形成されたフィールドプレート電極(8)とを有するパワー半導体素子。  (もっと読む)

(もっと読む)

LDMOSトランジスタを含む半導体装置

【課題】 LDMOSトランジスタを高耐圧にするとともに、オン抵抗を低減させる。

【解決手段】 半導体装置100は、P型シリコン基板102と、P型シリコン基板102上に形成されたゲート電極120と、ゲート電極120の横方向に形成されたドレイン(第二N型拡散領域109)と、ドレイン(第二N型拡散領域109)上に形成されたドレイン電極130と、ゲート電極120とドレイン電極130との間に設けられ、ゲート絶縁膜112よりも膜厚の厚い絶縁膜(フィールド酸化膜106)と、前記絶縁膜上において、ドレイン電極130に沿って形成された電界制御電極118と、により構成されたLDMOSトランジスタを含む。

(もっと読む)

エンハンスメントモード金属酸化膜半導体電界効果トランジスタ及びその形成方法

注入フリーエンハンスメントモード金属酸化膜半導体電界効果トランジスタ(EMOSFET)を提供する。EMOSFETは、III−V化合物半導体基板と、III−V化合物半導体基板上のエピタキシャル層構造とを有する。エピタキシャル材料層は、チャネル層と、少なくとも1つのドープ層とを有する。ゲート酸化膜層は、エピタキシャル層構造の上にある。EMOSFETは、更に、ゲート酸化膜層上の金属ゲート電極と、エピタキシャル層構造上のソース及びドレイン・オーミックコンタクトと、を含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能を向上させる。

【解決手段】 LDMOSFETのゲート電極30およびn+型ソース領域53上にサリサイド工程により金属シリサイド膜64を形成し、n-型オフセットドレイン領域33、n型オフセットドレイン領域51およびn+型ドレイン領域52上にはこの金属シリサイド膜を形成しない。ゲート電極30のドレイン側の側壁上には、絶縁膜を介して、シリコン膜からなるサイドウォールスペーサが形成され、このサイドウォールスペーサによりフィールドプレート電極44が形成される。フィールドプレート電極44はゲート電極30上に延在しておらず、サリサイド工程ではゲート電極30の上面の全面に金属シリサイド膜64が形成される。

(もっと読む)

強化された遮蔽構造を備えた金属酸化膜半導体デバイス

【課題】強化された遮蔽構造を備えた金属酸化膜半導体(MOS)デバイスを提供すること。

【解決手段】MOSデバイスは、基板上に形成された半導体層を含み、その基板は水平面とその水平面に垂直な方向の法線とを画定する。第1のソース/ドレイン領域および第2のソース/ドレイン領域が、半導体層内で、その上面近傍に形成され、第1のソース/ドレイン領域と第2のソース/ドレイン領域は互いに離隔されている。ゲートが、半導体層の上面近傍に形成され、少なくとも部分的には第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に配置される。第1の誘電領域が、MOSデバイス内に形成され、半導体層の上面から下方に第1の距離まで半導体層の中へ延在するトレンチの境界を画定し、第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に形成されている。

(もっと読む)

高電圧MOSFET用リサーフ拡散の方法

高電圧半導体装置用のウエハーが、先ず砒素をP型シリコン基板ウエハーの上面に約0.1ミクロンの深さまで注入することによって形成される。次にN型の非傾斜エピタキシャル層が、砒素が意図的に動かされないように、どんな拡散工程も無しに基板上に成長させられる。次に装置の接合がエピタキシャル成長層中に拡散させられる。 (もっと読む)

高圧NMOSトランジスタおよび製造方法

深いp型ウェル(DP)内のn型ドープされたソース領域(2)、チャネル領域(13)、有利にはゲート酸化膜(8)によって絶縁されたゲートフィールドプレート(6)の下方にある、対抗ドーピング領域(12)によって形成されたドリフト領域(14)および深いn型ウェル(DN)内に配置されたn型ドープされたドレイン領域(3)はこの順番で、基板(1)の上面に配置されている。 深いp型ウェル(DP)と深いn型ウェル(DN)の間のラテラル方向結合部(11)は、ドリフト区間(14)において、ドレイン領域(3)の近傍に設けられており、これによって、チャネル領域(13)内での高い電圧降下がトランジスタ領域内で回避され、高い閾値電圧並びに高いブレークダウン電圧がソースとドレインの間で得られる。  (もっと読む)

(もっと読む)

窒化物含有半導体装置

【課題】 ゲート絶縁膜と半導体層との間に良好な界面が形成され、ゲートリーク電流の小さい窒化物含有半導体装置を提供する。

【解決手段】 本発明の実施の一形態に係る窒化物含有半導体装置は、チャネル層として形成されたノンドープの第1の窒化アルミニウムガリウム(AlxGa1−xN(0≦x≦1))層と、第1の窒化アルミニウムガリウム層上にバリア層として形成されたノンドープ又はn型の第2の窒化アルミニウムガリウム(AlyGa1−yN(0≦y≦1,x<y))層と、第2の窒化アルミニウムガリウム層上にゲート絶縁膜下層として形成された窒化アルミニウム(AlN)膜と、窒化アルミニウム膜上にゲート絶縁膜上層として形成された酸化アルミニウム(Al2O3)膜と、第2の窒化アルミニウムガリウム層にそれぞれ電気的に接続されるように第1及び第2の主電極として形成されたソース電極及びドレイン電極と、酸化アルミニウム膜上に制御電極として形成されたゲート電極と、を備えているものである。

(もっと読む)

半導体装置

【課題】 高電圧駆動のMISトランジスタを有する半導体装置であって、耐圧の向上と、微細化の向上が図られた半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10の上方に設けられたゲート絶縁層20と、

前記ゲート絶縁層20の上方に設けられたゲート電極22と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28a,bと、

前記ゲート電極22と電気的に接続されたフィールドプレート電極44と、

前記フィールドプレート電極44を覆う絶縁層と、を含み、

前記絶縁層は、比誘電率が異なる領域を有し、比誘電率が高い領域は、前記導電層の一の端部に接している。

(もっと読む)

161 - 180 / 186

[ Back to top ]