Fターム[5H420NA21]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 基準生成部 (1,182) | 基準生成形式 (1,136) | バイポーラトランジスタを用いるもの (246)

Fターム[5H420NA21]の下位に属するFターム

電流制限回路 (8)

バンドギャップ電圧を利用するもの (218)

Fターム[5H420NA21]に分類される特許

1 - 20 / 20

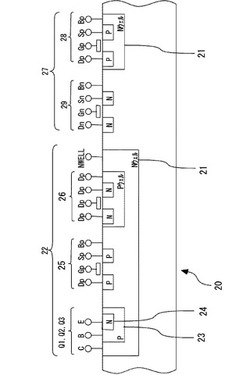

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

定電流回路の出力設定装置

【課題】電流値の設定が容易であり、且つ、装置構成を簡素化することが可能な定電流回路の出力設定装置を提供する。

【解決手段】基準電流Irefを流す基準電流発生回路11と、基準電流Irefに比例した電流を流すカレントミラー回路を少なくとも一つ備えた、4個のカレントミラー回路群、即ち、第1〜第4のカレントミラー回路群21〜24を備える。そして、各カレントミラー回路群21〜24は、それぞれ、基準電流Irefに対してα倍、2α倍、4α倍、8α倍となる電流を出力する。そして、各カレントミラー回路群を適宜選択して負荷に接続することにより、該負荷に供給する電流値が所望の電流値となるように設定することが可能となる。このため、操作性を容易とし、且つ、装置構成を簡素化することが可能となる。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

基準電圧発生回路とこれを用いた駆動装置、プリントヘッド及び画像形成装置

【課題】電源電圧の変動による基準電圧の変動を抑制し、駆動電流の変動をなくして印刷濃度むらを防止する。

【解決手段】基準電圧発生回路60では、PMOS61a,61bからなる第1のカレントミラー回路とNMOS61c,61dからなる第2のカレントミラー回路とを縦続接続して構成したカレントミラー回路部61を用いて、NPNTR65,66を駆動する構成にしている。そのため、カレントミラー回路部61の出力側のノードN3とノードN4の電位を略等しくすることができる。これにより、電源電圧VDDの値が変化しても、NPNTR66のコレクタ電位の変動を僅少にでき、基準電圧発生回路60から出力される基準電圧Vrefの変動を無視しうる程度にまで減少させることができる。

(もっと読む)

半導体集積回路装置

【課題】1次の温度依存性だけではなく、2次以上の温度依存性を補正することにより、高精度のクロック信号を生成する。

【解決手段】シリコンのp−n接合ダイオードの順方向電圧Vbe0が負の1次温度係数をもつこと、電流密度の異なるp−n接合ダイオードの順方向電圧の差(Vptat=Vben−Vbe0)が正の1次温度係数をもつことを利用し、正の1次の温度係数をもった電流Iptatと1次の温度係数が小さい電流I0を生成させ、抵抗R10とバイポーラのトランジスタQ10〜Q13からなる電流生成部に、電流I0,Iptatを加算および減算することにより、正の2次温度係数をもった電流Iptat2を生成し、これを用いて正の2次温度係数をもった基準電圧を生成することができる。

(もっと読む)

カレントミラー回路

【課題】低電圧での動作を可能とし、アーリー効果による電流比の悪化を抑圧可能とする。

【解決手段】

NPN型の第1及び第2のトランジスタ1,2のベース、第1のトランジスタ1のコレクタ、及び、デプレッション型のNチャンネルMOSトランジスタである第3のトランジスタ3のゲートが相互に接続されると共に、定電流源4に接続される一方、第1及び第2のトランジスタ1,2のエミッタは、共にグランドに接続され、第2のトランジスタ2のコレクタは、第3のトランジスタ3のソースに接続されて、この第3のトランジスタ3のドレインに出力可能に構成されてなり、低電圧での動作を可能とし、アーリー効果による電流比の悪化が抑圧可能となっている。

(もっと読む)

基準電圧発生回路

【課題】高耐圧のデプレッション型MOSトランジスタを用いることなく耐圧を高めるとともに、占有面積および消費電流の増加を抑制することができる基準電圧発生回路を提供する。

【解決手段】デプレッション型のMOSトランジスタ(Q1)とエンハンスメント型のMOSトランジスタ(Q2)とを直列形態に接続してなる基準電圧回路(11)を備えた基準電圧発生回路において、基準電圧回路の電源端子と前記MOSトランジスタの耐圧よりも高い電源電圧が印加される第1の電源電圧端子との間に接続された前記通常の耐圧よりも高い耐圧を有するクランプ用MOSトランジスタ(Q3)と、該クランプ用MOSトランジスタのゲート端子に印加されるバイアス電圧を生成するバイアス回路(12)とを設け、基準電圧回路の電源端子にバイアス電圧に応じてクランプされた電圧を供給するようにした。

(もっと読む)

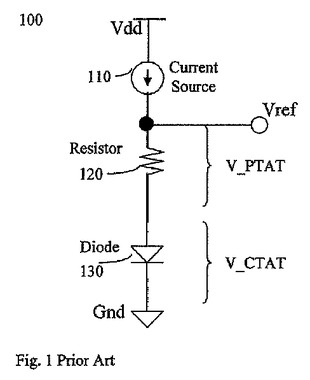

バンドギャップ基準電圧の二次補正回路および方法

より正確なバンドギャップ基準電圧を得るための、一次および二次誤差が同時に補正されるシステムおよび方法が提供される。一次誤差の補正に含まれる成分を用いることによって二次誤差が補正されて、有利なことにはプロセス変動が少なくなる。  (もっと読む)

(もっと読む)

カレントミラー回路

【課題】本発明は、電源急変時に生じる出力電流の変動を抑制することが可能なカレントミラー回路を提供することを目的とする。

【解決手段】本発明に係るカレントミラー回路は、入力電流Iinをミラーして第1ミラー電流I1を生成する第1カレントミラー段(トランジスタQa、Qb)と、電源急変時に生じる第1ミラー電流I1の増加分に応じた補正電流I3を生成し、これを第1カレントミラー段の出力端から引き込むピーク電流吸収回路Y(トランジスタQc、Qd、抵抗Ra、Rb)と、を有して成り、第1ミラー電流i1から補正電流I3を差し引いて得られる差分電流(=I1−I3)を出力電流Ioutとして後段回路(オペアンプAMP)に出力する構成とされている。

(もっと読む)

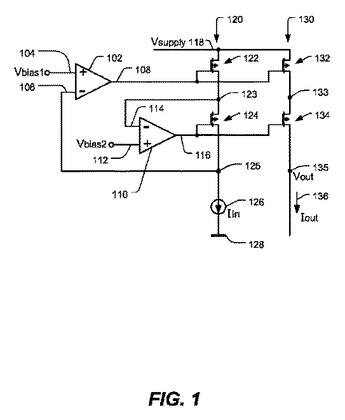

電流ミラー装置および方法

ある実施形態で、第1のトランジスタ対および第2のトランジスタ対を含む電流ミラーを備える回路が開示される。第1のトランジスタ対は第1のトランジスタおよび第2のトランジスタを含む。第2のトランジスタ対はカスコードトランジスタを含む。この回路は、第1のトランジスタおよび第2のトランジスタの両方に結合された出力を有するオペアンプも備える。  (もっと読む)

(もっと読む)

定電圧発生回路および定電圧発生方法

【課題】負荷となる利得可変増幅回路の負荷電流が増加するような場合であっても、所望の定電圧を出力可能な定電圧発生回路を提供する。

【解決手段】定電圧発生回路の出力回路として、あらかじめ定めた値まで低減した低出力インピーダンスの回路構成とするために、1ないし複数個のトランジスタTF1,TF2,TF3を並列接続してなるエミッタフォロア回路を用いる。トランジスタTF1,TF2,TF3の並列接続数を、負荷となる利得可変増幅回路で流れる負荷電流の電流レベルに応じた任意の値に設定する。また、出力回路に、出力電圧微調整用のトランジスタTE1,TE2,TE3またはダイオードを、エミッタフォロア回路と電源電圧端子との間に、出力電圧の微調整レベルに応じて1ないし複数個挿入する。エミッタフォロア回路用または出力電圧微調整用のトランジスタとして、バイポーラトランジスタまたは電界効果型トランジスタのいずれかを用いる。

(もっと読む)

定電流源及び近接センサ用集積回路装置

【課題】より小さな回路面積で温度特性に優れた定電流源及び近接センサ用集積回路装置を提供する。

【解決手段】集積回路化された定電流源は、一方をコレクタ及びベースの接続されたマスター側トランジスタQ0とし他方をスレーブ側トランジスタQ1とするカレントミラー回路11で構成される。カレントミラー回路は、マスター側トランジスタのエミッタ及びスレーブ側トランジスタのエミッタが、それぞれインプラ抵抗RH及びベース拡散抵抗RBを介して第1の所定電圧の供給される第1電源線X1に接続され、インプラ抵抗RHの抵抗値が、ベース拡散抵抗RBの抵抗値よりも大きく設定され、マスター側トランジスタのコレクタが、その流れる電流を制限するための制限用インプラ抵抗RH0を介して第2の所定電圧の供給される第2電源線X2に接続され、定電流源の供給電流を、スレーブ側トランジスタに流れる電流I1とした。

(もっと読む)

半導体集積回路装置

【課題】微細化されたMOSFETに好適な基準電圧発生回路を有する半導体集積回路装置を提供する。

【解決手段】第1電流密度とされる第1トランジスタと第1電流密度よりも小さな第2電流密度とされる第2トランジスタのベースを共通接続し、そのコレクタ差電圧に対応した出力電圧を増幅回路で形成して上記ベースに帰還する。第1抵抗素子に上記第1と第2トランジスタのベース,エミッタ間差電圧を印加して基準電流を形成する。上記基準電流に対応した電流を上記第1、第2及び第3トランジスタに供給する。上記第3トランジスタのベースとコレクタとを共通接続し、第2抵抗素子を直列形態に接続する。上記第3トランジスタのサイズ及び上記第1及び第2抵抗素子の抵抗値の設定により、上記第3トランジスタ及び第2抵抗素子で発生する電圧が、上記第1及び第2電源電圧及び温度変化に対して一定の基準電圧となるようにする。

(もっと読む)

電流源回路

【課題】温度依存性をほとんど持たない出力電流を得ることができ、かつ駆動端子電圧に比例した出力電流を得ることができる電流源回路を提供する。

【解決手段】温度依存性をもつ電圧を出力する電圧発生回路11と、該電圧発生回路11から出力する前記温度依存性をもつ電圧を入力して温度依存性をもたない電流を出力する電圧−電流変換回路12と、前記電圧発生回路11および電圧−電流変換回路12に駆動端子電圧を供給する電圧発生回路20とを備え、電圧発生回路20から供給する駆動端子電圧の変化に応じて、電圧−電流発生回路12の出力電流が線形的に変化するようにした。

(もっと読む)

バンドギャップ回路

【課題】スイッチトキャパシタ型のバンドギャップ回路において、容量の占有面積を増やすことなく、熱電圧に乗じる係数をより細かく設定すること。

【解決手段】第1のスイッチトキャパシタ回路2のオペアンプ回路OP3の入力端子と、第2のスイッチトキャパシタ回路3のオペアンプ回路OP4の出力端子を、結合容量C7により結合する。結合容量C7の容量値は第1のスイッチトキャパシタ回路2のフィードバック容量C6の容量値よりも小さい。各スイッチトキャパシタ回路2,3の各入力容量C5,C8および各フィードバック容量C6,C9と、結合容量C7の各容量値により決まる係数を熱電圧に乗じて得た、絶対温度に比例するPTAT電圧を、電圧発生回路1で発生した、温度の上昇にともなって電圧値が減少する負の温度依存性を有するpn接合の順方向電圧に加算することによって、温度に依存しない基準電圧を発生させる。

(もっと読む)

低消費電力回路

【課題】 起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】 カレントミラー回路M1と、カレントミラー回路M1の出力端に一端を接続した第1分割抵抗R1、この第1分割抵抗R1に一端を接続した第2分割抵抗R2との直列回路からなるバイアス分割回路R12と、第1分割抵抗R1の一端に制御端子(ゲート端子)を、第2分割抵抗R2の他端に第2主電流端子を、GNDに第1主電流端子を接続した第1トランジスタN1と、第2分割抵抗R2の他端に制御端子(ゲート端子)を、カレントミラー回路M1の入力端に第2主電流端子を、第2主電源GNDに第1主電流端子を接続した、第1トランジスタN1と同一チャネル導電型の第2トランジスタN2とを含み、起動時に第1分割抵抗R1と第2分割抵抗R2との接続ノードに起動電流ISTを印加する。

(もっと読む)

半導体装置

【課題】本発明は、外部端子の状態に依らず、その内部回路を確実に動作させてシステムの破綻を未然に回避することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、入力電流i1に応じた出力電流i2をIC内に供給する内部電流生成部1と、内部電流生成部1の入力端側に外部抵抗Rexを接続するための外部端子2と、内部電流生成部1の入力端と端子2との間に接続された電流制限素子3と、電流制限素子3の一端電圧VAが第1閾値電圧VBより高いときに入力電流i1を引き込む第1電流制限部4と、外部端子2の端子電圧VCが第2閾値電圧より高いときに入力電流i1を引き込む第2電流制限部5と、を有して成る。

(もっと読む)

全npnトランジスタPTAT電流源

本発明は、改良されたPTAT電流源と、PTAT電流を生成するためのそれぞれの方法とに関する。適切なコレクタ電流が、トランジスタのベース−エミッタ電圧とコレクタ電流の間の対数関係を利用する2つのトランジスタにおいて生成され、強制される。前記2つのトランジスタのベース端子の間に接続された抵抗器が、同じまたは異なる面積のどちらかをもち得る2つのトランジスタのベース−エミッタ電圧の間の電圧差を感知する。抵抗器を流れる電流の一部は、トランジスタのコレクタへと強制され、出力電流を提供するために出力トランジスタによってミラーされる。この原理によって、従来のPTAT電流源でのようにpnpトランジスタを必要としない、全npnトランジスタPTAT電流源が、提供されることができる。本発明は一般に、PTAT電流基準を必要とする、様々な異なるタイプの集積回路に適用可能である。  (もっと読む)

(もっと読む)

定電流回路及びその定電流回路を使用したシステム電源装置

【課題】 製造プロセスの変動や温度変動に対する変動を低減させて高精度の複数の定電流を生成しバイアス電流として供給することができる定電流回路及びその定電流回路を使用したシステム電源装置を得る。

【解決手段】 PMOSトランジスタM1及びM2から流れる各電流i1及びi2の一方の電流の変動に対して負帰還がかけられてその変動を打ち消すように、演算増幅回路AMPがPMOSトランジスタM1及びM2の動作制御を行い、PMOSトランジスタM1及びM2から対応して電流が供給される2つのpnpトランジスタQ1及びQ2に流れる電流密度の差によって生じる電位差に接続した抵抗R1に流れる定電流を基準電流とし、演算増幅回路AMPによって動作制御されたPMOSトランジスタMA1〜MAnで該基準電流に比例した各電流をそれぞれ生成して出力するようにした。

(もっと読む)

絶対温度に比例する電圧回路

第1の入力と第2の入力を有し、かつカレントミラー回路を駆動する出力を有する第1の増幅器を備える電圧回路が提供される。カレントミラー回路からの出力は、増幅器の第1の入力および第2の入力にそれぞれ結合された第1のトランジスタおよび第2のトランジスタを駆動する。増幅器が第1のトランジスタのベースとコレクタを同じ電位に保つように、第1のトランジスタのベースは増幅器の第2の入力に結合され、10第1のトランジスタのコレクタは、増幅器の第1の入力に結合されている。第1のトランジスタおよび第2のトランジスタは、第1のトランジスタと第2のトランジスタのベース−エミッタ電圧の差が第2の15トランジスタに結合された負荷抵抗の両端間に発生することができるように異なる電流密度で動作するように適合されており、ベース−エミッタ電圧の差はPTAT電圧である。  (もっと読む)

(もっと読む)

1 - 20 / 20

[ Back to top ]