Fターム[5H730AA15]の内容

DC−DCコンバータ (106,849) | 目的 (10,886) | 大容量化、小型軽量化、コスト改善 (1,769)

Fターム[5H730AA15]の下位に属するFターム

素子、回路の並列化、分割化によるもの (167)

Fターム[5H730AA15]に分類される特許

1,581 - 1,600 / 1,602

デジタル変調を用いるデジタルDC−DCコンバータ

デジタルDC−DCコンバータは、A/D変換よりも1次デルタ−シグマモ変調を用いて実現される。このDC−DCコンバータにおいて、PWM発生器210は、入力されるPWM信号に応じて入力される直流電圧Vinを予め設定された大きさの直流電圧に変換する。コンバータ220は、PWM発生部210から出力される直流電圧を予め設定された電圧に変換する。デルタ−シグマ変調部230は、コンバータ220の出力電圧Voutに相当するフィードバック電圧Vfdを、予め設定された基準電圧Vrefに応じて1ビットのデジタル電圧Voに変換する。カウンタ240は、デルタ−シグマ変調部230の1ビットデジタル電圧Voに含まれたロジック1をカウントする。ディレー制御部250は、カウンター240によってカウントされたロジック1の個数に応じて高レベルの遅延時間を制御し、この制御された高レベル遅延時間を有するPWM信号をPWM発生器210に出力する。 (もっと読む)

多用途のインテリジェントな電源コントローラ

本発明は、主要供給源または補助供給源のどちらかから拡張カード上の回路についての様々な電圧を供給することが可能なモノリシックな高度に集積された電源回路を実現する。このモノリシック電源回路は、2つのスイッチング・コンバータ、2つの低ドロップアウト・レギュレータ、スタンバイ・レギュレータ、リセット回路、および制御回路を含んでいることが好ましい。モノリシックな電源回路を介して様々な電圧を供給するための関連する方法についても開示される。

(もっと読む)

(もっと読む)

給電切替えを組み込んだスイッチング電源コントローラ

本発明は、わずか2つのハイサイドのスイッチング・トランジスタおよび1つのローサイドの整流デバイス、ならびに制御回路を備える、スイッチング・コンバータを提供する。このスイッチング・コンバータは、主給電源または補助給電源で動作することができる。本発明はさらに、2つのハイサイドのスイッチング・トランジスタおよび1つのローサイドの整流デバイスによって、第1の供給電圧および第2の供給電圧から調節された電圧を発生させる方法を含む。

(もっと読む)

(もっと読む)

コンデンサ容量式点火装置

DC−DCコンバータのトランス5に点火用コンデンサC1への電圧供給用2次巻線5bとは別個の第2の2次巻線5cを設け、第2の2次巻線をスイッチング回路を介して点火時期制御回路9に接続する。スイッチング回路は、発電機の発電電圧が所定電圧より低い場合又は発電機の回転速度が所定値よりも低い場合には、点火時期制御回路に対して第2の2次巻線により電力を供給し、逆の場合には、点火時期制御回路に対して発電機の出力端子側から電力を供給する。これにより、バッテリ無し等の状態でエンジン回転速度が低く発電機の発電電圧が低い場合であっても点火時期制御回路を動作させることができると共に、エンジン回転速度が高い場合に発電電圧を無駄なく点火用に用いることができる。エンジン回転速度が高い場合の効率的な発電エネルギの消費が可能であることから、大型の回路や素子を用いる必要が無いため装置を小型化し得る。 (もっと読む)

スイッチング電源装置

第1のスイッチング制御回路(CNT1)は整流ダイオード(Ds1)が非導通状態となり、トランス電圧Vtが反転するタイミングをトリガとして所定の遅延時間の後に第1のスイッチ素子(Q1)をターンオンさせる。第2のスイッチング制御回路(CNT2)は第1のスイッチ素子(Q1)のターンオフによりトランス電圧Vtが反転するタイミングをトリガとして第2のスイッチ素子(Q2)をターンオンさせる。第3のスイッチング制御回路(CNT3)は第2のスイッチ素子(Q2)のターンオフをトリガとして第3のスイッチ素子(Q3)をターンオンさせる。(CNT1)は第1出力電圧Vo1が所定値になるように第1のスイッチ素子(Q1)の期間ton1を定め、(CNT2)は第2出力電圧Vo2が所定値になるように第2のスイッチ素子(Q2)のオン期間ton2を定め、さらに(CNT3)は第3出力電圧Vo3が所定値になるように第3のスイッチ素子(Q3)のオン期間ton3を定める。 (もっと読む)

スイッチング電源装置

トランス(T)の1次巻線(Lp)に直列に第1のインダクタ(Lr)を接続し、第1のスイッチ回路(S1)のオン期間に交流入力電圧を整流した正弦波状のキャパシタ(Ca)の電圧が印加されるように第2のインダクタ(Li)を設ける。また第2のインダクタ(Li)に対する逆電流を阻止するダイオード(

Di)と、第2のインダクタ(Li)に蓄積された励磁エネルギーにより充電され且つ第1のスイッチ回路(S1)のオン期間において1次巻線(Lp)に電圧を印加するキャパシタ(Ci)を設ける。さらにインダクタ(Lr)と1次巻線(Lp)と第2のスイッチ回路(S2)とともに閉ループを構成するようにキャパシタ(Cr)を設ける。スイッチング制御回路(SC1),(SC2)は、第1のスイッチ素子(Q1)のオン期間を制御して出力電圧Voを制御し、第2のスイッチ素子(Q2)のオン期間によって入力電圧Viを制御する。

(もっと読む)

スイッチング電源装置

スイッチ素子(Q1),(Q2)、ダイオード(D1),(D2)、キャパシタ(Cds1),(Cds2)からなる第1・第2のスイッチ回路(S1),(S2)と、トランス(T)を備え、トランス(T)の1次巻線(Lp)に直列に第1のインダクタ(Lr)を接続し、第1のスイッチ回路(S1)のオン期間に第3のキャパシタ(Ca)の電圧が印加されるように第2のインダクタ(Li)を設ける。また(Li)に対する逆電流を阻止するダイオード(Di)と、(Li)に蓄積された励磁エネルギーにより充電され且つ(S1)のオン期間において1次巻線(Lp)に電圧を印加するキャパシタ(Ci)を設ける。さらにインダクタ(Lr)と1次巻線(Lp)と第2のスイッチ回路(S2)とともに閉ループを構成するようにキャパシタ(Cr)を設ける。 (もっと読む)

DC/DCコンバータを区分化スイッチングで調整するためのデジタル・ループ

区分化されたスイッチ、フライイング・キャパシタ、出力電圧端子、フィードバック・ループ、及び、デジタル電圧調整器ブロックを含むスイッチ・アレイ、を含む電力制御回路が提供される。デジタル電圧調整器ブロックは、A/Dコンバータ、エンコーダ、加減算器、及び、ゲート・ロジックを含む。これらの電力制御回路は、パス・トランジスタを含まない。電力制御回路の荷電ポンプが、荷電フェーズ、及び、ポンピング・フェーズを含む2フェーズ周期で作動する方法もまた提供される。電力制御回路は、これらのフェーズの双方で制御され、それによって、出力電圧のリップルを削減する。  (もっと読む)

(もっと読む)

制御を改善した電力変換装置

本発明の実施形態より、電力変換装置は、一次巻線、及び二次巻線を持つ変圧器を含む。一次巻線は、入力電圧を受け取るように結合され、二次巻線は、出力電圧を提供する。変圧器の一次巻線に結合されたトランジスタは、その一次巻線を通って流れる電流を制御する。トランジスタに結合された電流検出デバイスは、電力変換装置を通って流れる電流の量を示す信号を作り出す。電流検出デバイスは、電力変換装置における電流制御ループの一部を形成する。変圧器の二次巻線に結合されたフィードバックコントローラは、電力変換装置の出力電圧を示す信号を提供する。フィードバックコントローラは、電力変換装置における電圧制御ループの一部を形成する。コントローラは、電流制御ループのアナログ制御、及び電力変換装置の電圧制御ループのデジタル制御を提供するように動作可能である。  (もっと読む)

(もっと読む)

電流調節充電ポンプドライバにキャパシタ比例電流を与える集積デバイス

集積回路(10)は、外部電流検出抵抗を必要とすることなく、バッテリ(18)から負荷へ流れる電流を調節する。そのICは、主充電ポンプ(12)、モデル充電ポンプ(14)、電流検出回路(U3,M2)、モデル充電ポンプの出力部での電圧レベルを主充電ポンプの出力部での電圧に等しくさせる第1の制御回路と、および、モデル充電ポンプによるモデル電流出力を、バッテリ電源の電圧変化に拘わらず、外部フライイングキャパシタ(Cp)のキャパシタンス値により確立されたレベルに調節させるための第2の制御回路とを備える。 (もっと読む)

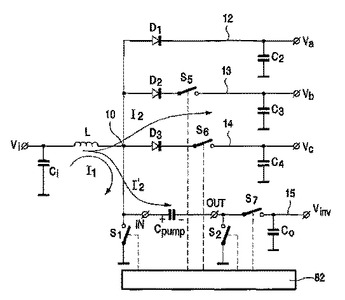

電圧変換器

誘導性磁化モードにおいてエネルギを蓄積するとともに、誘導性減磁モードにおいてエネルギを転送する誘導性回路(L)を電圧変換器が備える。加えて、当該電圧変換器は、少なくとも2つの非反転出力電圧(Va,Vb,Vc)を提供する少なくとも2つの非反転分岐(12,13,14)と、反転出力電圧を提供する反転分岐(15)と、を備える。前記反転分岐(15)及び前記非反転分岐(12,13,14)は、前記誘導性回路(15)の出力(10)に並列接続される。前記誘導性回路は、前記反転分岐(15)へ及び前記少なくとも2つの非反転分岐(12,13,14)のうちの1つへエネルギを転送する。これにより、前記反転電圧(Vinv)及び前記少なくとも2つの非反転分岐(12,13,14)のうちの前記1つの対応する非反転出力電圧(Va,Vb,Vc)が、逆の極性及び略等しい大きさを有している。  (もっと読む)

(もっと読む)

電源制御システムのスタートアップ方法および回路

本発明の電源制御システム(70)は、電源制御システムのスタートアップ動作を制御するために2つの別個の電流を用いる。電流の1つは小さな値を有し、初期値まで出力電圧を印加するために使用される。一旦初期値に到達すると、大きな値を有する第2の電流が動作電圧値まで出力電圧を印加するために使用される。  (もっと読む)

(もっと読む)

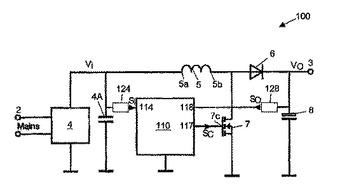

デジタル信号プロセッサを備えたパワーコンバータ

アップコンバータ(100)は、出力(3)と直列に接続されたインダクタ(5)及びダイオード(6)と、前記出力と並列に接続されたコンデンサ(8)と、前記インダクタと前記ダイオードとの間のノードに結合された1つのスイッチ端子を持つ制御可能スイッチ(7)とを有する。制御方法は、−インダクタに整流化された交流電圧(Vi)を供給するステップと、−スイッチをスイッチ開閉するために、パルス幅(TH)を持つスイッチ制御信号(SC)を発生させるステップと、を有し、スイッチ制御信号は、出力(3)における出力電圧(VO)に基づいて発生させられる。本発明によれば、アップコンバータは、デジタルプロセッサ(110)を有し、該デジタルプロセッサ(110)は、出力電圧(VO)をサンプリングし、出力電圧(VO)が略一定に留まるようにスイッチ制御信号(SC)のパルス幅(TH)を計算するように、サンプリングされた出力電圧(VO)をデジタル的に処理する。  (もっと読む)

(もっと読む)

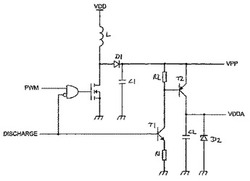

強化されたトランジスタ駆動装置の電荷回収

エレクトロルミネセントディスプレイ用の制御回路であって、フライバックコンバータとH−ブリッジとを用いて低電圧DC源から容量負荷に高電圧交流電流を提供する。容量負荷の極性が反転するたびに、容量負荷が放電する。この高電圧放電を低電圧コンデンサに蓄えて、制御回路のスイッチング素子の電力源となる補助電源として使用する。 (もっと読む)

面積効率の高い電荷ポンプ

第1の電荷ポンプが電圧加算器段を複数備える。第1の電圧加算器段は、入力電圧信号VCCを受け取り、クロック信号に応答して2* VCCとVCCとの間を交番する第1の電圧信号を出力する。N番目の電圧加算器段は先行段から入力電圧信号VCCと第1の電圧信号を受け取り、N* VCCとVCCとの間で交番する第2の電圧信号を出力する。個々の加算器段内に設けられるコンデンサはVCCの最大使用電圧を維持するように要求される。別の実施形態では、第1の電荷ポンプを1以上の倍電圧器段と組み合わせて、さらに高い出力電圧の発生を図るようにしてもよい。  (もっと読む)

(もっと読む)

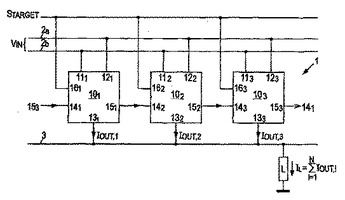

スイッチモード電源

複数の電源モジュール10を有するスイッチモード電源アセンブリ1が記載され、それぞれの電源モジュール10は、巡回的に互いに結合される。それぞれの電源モジュール10iは、全てのモジュールのインタリーブ動作を保証するために、次の隣のモジュール10i+1のための同期制御信号を発生し、前の隣のモジュール10i+1からの同期制御信号を受けるための同期制御手段を有する。低電力モジュールをハイボリュームで比較的容易に製造可能である。

(もっと読む)

(もっと読む)

電圧降圧装置を有する電気ケーブルおよびコネクタ組立

【解決手段】12ボルト供給導体および5ボルト供給導体を有する電気ケーブルと、この電気ケーブルに接続された電気コネクタとを有する電気ケーブルおよびコネクタ組立。前記電気コネクタは、12ボルト供給導体と、5ボルト供給導体に接続された5ボルト供給接点と、電気コネクタのハウジングの内に位置された電圧降圧装置によって5ボルト供給導体に接続された3.3ボルト供給接点とを有する。 (もっと読む)

燃料電池及び燃料電池の電圧制御方法、並びに携帯端末

【課題】無負荷から定格電流までの範囲内では電池電圧に関わらず一定電圧を出力し、また、電池電圧より高い電圧を出力できる燃料電池を提供する。

【解決手段】燃料電池単体1は、降電圧型定電圧回路2を介して負荷3を接続している。降電圧型定電圧回路2は、スイッチング回路によって定電圧制御を行う。したがって、燃料電池単体1の出力電流−出力電圧が非直線な特性であっても、昇電圧型定電圧回路4のコンデンサ15から負荷3へは、燃料電池単体1の出力電圧より低い一定電圧が出力される。よって、無負荷時であっても燃料電池単体1の過電圧が負荷3へ印加されることはない。また、降電圧型定電圧回路2から出力する一定電圧のレベルは、制御回路16の電圧調整器17によって任意に可変できる。尚、降電圧型定電圧回路2を昇電圧型定電圧回路に置き換えれば、燃料電池単体1の電池電圧より高い電圧を出力することができる。

(もっと読む)

圧電トランス駆動装置

【課題】圧電材料を圧電トランス構成にしたときに、ほぼ半値に低下する圧電セラミックス材料特性値の、機械的品質計数Qm値を、ハイQm値とした圧電トランスを得る。

【解決手段】少なくても2枚ないし多くとも3枚の圧電トランスの、それぞれの電極部が合わさるように重ね合わせて、高温度で焼成或いは銀焼成或いはリフローすることにより、前記圧電トランスが相互に固着して、一体構成されて完成されていて、ハイQmを得ることを特徴とする圧電トランスを実現した。

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

1,581 - 1,600 / 1,602

[ Back to top ]