Fターム[5J001BB12]の内容

Fターム[5J001BB12]に分類される特許

161 - 180 / 420

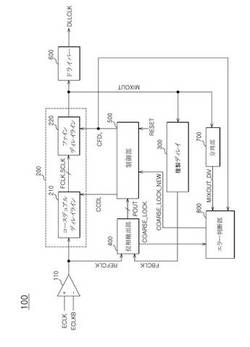

遅延ロックループ回路及びその制御方法

【課題】本発明は、動作環境が変化しても、遅延ロックの所要時間の増加を防止できる遅延ロックループ回路及びその制御方法を提供する。

【解決手段】本発明は、基準クロック信号を遅延させて出力する遅延ラインと、基準クロック信号と前記遅延ラインの出力信号との位相差を検出して、位相検出信号及び第1の遅延モード判断信号を出力する位相検出部と、位相検出信号及び第2の遅延モード判断信号により、遅延ラインを制御するための遅延制御信号を出力する制御部と、遅延制御信号及び遅延ラインの出力信号により、第1の遅延モード判断信号のエラーを検出し、エラー検出結果により、第2の遅延モード判断信号を出力するエラー判断部を備える。

(もっと読む)

1/4周期遅延クロック発生器

【課題】リセット信号を別途に不要とし、特定の初期値がなくても正常に動作できる1/4周期遅延クロック発生器を提供する。

【解決手段】本発明の1/4周期遅延クロック発生器は、基準クロック信号を発生させる基準クロック発生部と、前記基準クロック信号の立ち上がりエッジで第1入力信号をキャッチして前記基準クロック信号の次の立ち上がりエッジまで第1出力信号として前記第1入力信号を出力し、反転された前記第1出力信号の入力を前記第1入力信号として受ける第1回路部と、第2入力信号をキャッチして第2出力信号として出力し、前記第2入力信号として前記第1回路部から前記第1出力信号の入力を受ける第2回路部とを備える。

(もっと読む)

整数および分数時間分解能を有するプログラマブル遅延回路

整数および分数時間分解能を有する遅延を与えることが可能なプログラマブル遅延回路が記載されている。一例示的設計では、装置は、第1および第2の遅延回路を含む。第1の遅延回路は、整数個のタイムユニットからなる第1の遅延を与える。第2の遅延回路は、前記第1の遅延回路と結合されて、1タイムユニットの分数の第2の遅延を与える。第1の遅延回路は、直列に結合された複数の単位遅延セルを含むことが可能である。各単位遅延セルは、イネーブル時に、1タイムユニットの遅延を与えることが可能である。第2の遅延回路は、第1および第2のパスを有することが可能である。第1のパスは、選択された場合には、短い遅延を与えることが可能であり、第2のパスは、選択された場合には、長い遅延を与えることが可能である。第2のパスは、第2のパスに長い遅延を得るために、追加負荷を与える少なくとも1個のダミー論理ゲートと結合可能である。  (もっと読む)

(もっと読む)

可変遅延回路及びその制御方法

【課題】遅延素子の最小遅延時間よりも短い遅延時間を設定し、遅延時間の設定精度を向上させることができる可変遅延回路及びその制御方法を提供する。

【解決手段】入力信号を遅延させる第1遅延素子20Oと、第1遅延素子を並列接続され、入力信号を遅延させる第2遅延素子40と、第1遅延素子の遅延量及び第2遅延素子の遅延量を調整する制御電流を供給する制御電流供給部50と、入力信号の遅延時間を選択する遅延時間選択信号S1に応じ、第1遅延素子の出力信号S1Aもしくは第2遅延素子の出力信号S1Bのいずれか一方を選択する出力信号選択部60と、を備える。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

半導体装置

【課題】電源電圧の変化、温度変化に対してタイミング変動の小さいタイミング制御回路、及び該回路を備えた半導体装置の提供。

【解決手段】入力クロックを用いた第1のクロック生成回路、及び第2のクロック生成回路と、前記第1のクロック信号と、前記第2のクロック信号と、コマンドデコーダから活性化信号と、タイミングレジスタから遅延時間を選択する選択信号とを受け、前記活性化信号の活性化から、前記選択信号によって規定される、前記第1の周期の所定倍(m)の時間と、前記第2の周期の所定倍(n)の時間とを合成した時間に対応したタイミング生成回路とを備え、タイミングレジスタはm、nの値を記憶し、タイミングレジスタに記憶するのは、モードレジスタセットコマンドの時の初期化シーケンスで実施する。動作状態では、前記のタイミングレジスタに記憶した情報をもとに、タイミング生成回路から所望のタイミングで、タイミング信号を出力する。

(もっと読む)

ノイズフィルタ回路、デッドタイム回路、遅延回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、制御回路、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60;80;100)は、入力信号(IN)に基づく信号を入力する第1のインバータ回路(12;62;82;102)と、入力信号(IN)に基づく信号を入力する第2のインバータ回路(14;64;84;104)と、第1および第2のインバータ回路(12、14;62、64;82、84;102、104)からの信号に基づく信号を、セット信号(S)及びリセット信号(R)として入力するラッチ回路(16;66;86;106)と、を備える。第1および第2のインバータ回路(12、14;62、64;82、84;102、104)のそれぞれは、第1および第2の導電型のトランジスタを含み、第1および第2の導電型のトランジスタの一方の能力は、第1および第2の導電型のトランジスタの他方の能力より低い。

(もっと読む)

歪曲されたデューティ比を補正するDLLクロック生成回路

【課題】本発明は、デューティの歪曲を補正したDLLクロックを生成するDLLクロック生成回路を提供する。

【解決手段】本発明のDLLクロック生成回路は、 第1のクロック及び第2のクロックの入力により、第1の内部クロック及び第2の内部クロックを生成し、第1の内部クロックのデューティ比により生成された基準信号に基づき、第1の内部クロック及び第2の内部クロックのデューティを補正するデューティ補正バッファと、デューティ補正バッファに連結しており、第1の内部クロックのイネーブル動作により第1のレベルに遷移され、第2の内部クロックのイネーブル動作により第2のレベルに遷移される、DLLクロックを生成するエッジトリガー部を含む。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

発振開始検出回路及び半導体集積回路

【課題】チャージポンプ方式の発振開始検出回路において、プロセスのばらつき等に起因する誤動作を確実に防止する。

【解決手段】この発振開始検出回路は、発振回路によって生成される発振信号を入力して、所定の期間をおいて交互に活性化される第1の制御信号及び第2の制御信号を生成する制御信号生成回路と、第1の制御信号が活性化されているときにオン状態となる少なくとも1つのトランジスタ、及び、第2の制御信号が活性化されているときにオン状態となる少なくとも1つのトランジスタが直列に接続され、第1の電源電位から電荷を移送するトランジスタ列と、トランジスタ列に含まれている複数のトランジスタによって移送される電荷をそれぞれ蓄積する複数のコンデンサと、検出信号を生成する最終段のコンデンサの端子を第2の電源電位にプルダウン又はプルアップする抵抗とを含む。

(もっと読む)

パルス遅延回路及びその駆動方法、AD変換回路、時間測定回路

【課題】プロセス技術の高度化に依存することなく、A/D変換回路や時間測定回路の性能を向上させることが可能なパルス遅延回路、及びその駆動方法、更には、これを利用したA/D変換回路,時間測定回路を提供する。

【解決手段】遅延ユニットDUを構成するインバータ回路INVは、ゲートG同士,ドレインD同士が互いに接続されたPMOSトランジスタTp及びNMOSトランジスタTnからなる、いわゆるCMOSトランジスタであり、NMOSトランジスタTnのソースS及びバックゲートBを負極駆動端子105に接続(即ち接地)し、PMOSトランジスタTpのソースSを正極駆動端子103に接続(即ちアナログ入力信号Vinを印加)し、PMOSトランジスタTpのバックゲートBを、制御端子107に接続(即ち、制御信号としての固定電圧VDDを印加)する。

(もっと読む)

信号伝達回路

【課題】トランスを飽和させることなく、省電力で駆動させつつ、出力信号を正確に出力することが可能な信号伝達回路を提供することを目的とする。

【解決手段】1次側コイル及び2次側コイルを備えるトランス53と、入力信号の立上りタイミングにおいて1次側コイルに第1のパルス電圧を発生させるとともに、入力信号の立下りタイミングにおいて1次側コイルに第2のパルス電圧を発生させる駆動部56と、2次側コイルに第1のパルス電圧に対応するパルス電圧が発生すると出力信号を立上らせ、2次側コイルに第2のパルス電圧に対応するパルス電圧が発生すると出力信号を立ち下がらせる2次側回路52と、一定周期で1次側コイルに第3のパルス電圧を発生させる駆動回路3と、2次側回路52の出力先に異常が発生すると、2次側コイルに流れる電流を変動させる抵抗68及びMOSFET73とを備えて信号伝達回路1を構成する。

(もっと読む)

チャージドメインフィルタ回路

【課題】低消費電力で動作可能であり、フィルタ特性がリコンフィギュアラブルである、チャージドメインフィルタ回路を提供すること。

【解決手段】所定の間隔でサンプリングされる第1の信号を出力する第1の信号出力手段と、第1の信号からサンプリング間隔のn倍(nは自然数)遅れて、かつ連続したタイミングでサンプリングされる第2の信号を出力する少なくとも1つの第2の信号出力手段と、第2の信号出力手段において時間的に後にサンプリングが行われる一つの第2の信号からサンプリング間隔のn倍遅れたタイミングでサンプリングされる第3の信号を出力する第3の信号出力手段と、第1の信号、第2の信号、および第3の信号を加算して出力する加算手段と、を含み、第1の信号出力手段と第2の信号出力手段とに備えられるサンプリングキャパシタの容量比を連続的にまたは離散的に可変とするチャージドメインフィルタ回路が提供される。

(もっと読む)

遅延調整回路

【課題】遅延セルとして専用のハードマクロを必要とせず、かつ、遅延調整対象信号について高精度の遅延調整を行うことができる遅延調整回路を提供する。

【解決手段】位相比較器353で、セレクタ351なしに基準クロック信号REF_CLK1を1周期遅延させるのに必要な遅延セル348内のユニットセルの段数pと、ユニットセルの段数に換算したセレクタ351の遅延分qとを、基本情報として算出する。遅延制御器357で、クロック信号CLK及びデータ信号DATA1、DATA2を位相量θa°、θb°、θc°だけ遅延させるのに必要な遅延セル336、342、345内のユニットセルの段数wa、wb、wcを{(遅延位相量指示信号D_SETが指示する遅延位相量θa°、θb°又はθc°/360°)×p−q}という計算式で算出する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】クロックのデューティ検出において、半導体メモリ装置内のプロセス、電圧レベル、及び温度などによる環境変数の変化によって発生するオフセットを除去するための初期測定動作を行うことができる回路を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、初期測定動作時、共通クロックの遷移時点に対応する2つの検出パルスを生成するクロックエッジ検出部100Bと、前記2つの検出パルスを比較し、その結果を出力するデューティ検出部200Bと、前記初期測定動作時、デューティ検出部200Bから出力された比較結果に基づいて、デューティ検出部200Bを制御するコードカウンタ300とを備える。

(もっと読む)

調整可能デューティサイクル回路

【解決手段】回路によって生成される信号のデューティサイクルを調整及びプログラミングする技術が開示される。実施形態では、並行トランジスタはNANDゲートと電源電圧との間に結合される。前記並行トランジスタを選択的にイネーブルにすることはNANDゲートのスイッチングポイントを調整し、それにより出力信号のパルス幅の制御を可能にする。別の実施形態では、NANDゲートのPMOS対NMOSトランジスタのサイズは同じ効果を達成するために選択的に変えられる。更に測定二次相互変調結果及び/又は残差側波帯を最小化するために受信機を調整する技術のアプリケーションが開示されている。 (もっと読む)

半導体集積回路装置

【課題】本発明は、オペアンプを用いた遅延回路において、低電圧時でも所望の遅延量を作り出すことができるようにする。

【解決手段】たとえば、遅延素子部11は、インバータINV1の出力に応じて、キャパシタC1を充電させる。遅延素子部11とは相補的に動作する遅延素子部12は、インバータINV2の出力に応じて、キャパシタC2を放電させる。このとき、遅延素子部11に設けられた抵抗素子R1の抵抗値と、遅延素子部12に設けられた抵抗素子R2の抵抗値との比率を異ならせる。これにより、低電圧時にも、オペアンプ回路13を構成するNMOSトランジスタ13bのしきい値以上に、そのゲート−ソース間電圧Vgs2を確保できるようにする。

(もっと読む)

パルス発生回路およびUWB通信装置

【課題】立ち上がり、立ち下りのエッジで起動されたパルス間で振幅が異なり、正負の対称性がずれる。

【解決手段】起動信号を所定量の遅延を伴って論理反転する縦続接続された複数のインバータからなるインバータ遅延回路と、出力端子を、インバータ遅延回路の出力Di,XDi−1の論理積が真のとき第一の電位に接続し、出力Di,XDi+1の論理和が偽のとき第二の電位に接続する第一のスイッチ回路と、出力端子を、出力Di,XDi+1の論理積が真のとき第一の電位に接続し、出力XDi+1,Di+2の論理和が偽のとき第二の電位に接続する第二のスイッチ回路と、第一のスイッチ回路が活性化されるとき起動信号をインバータ遅延回路の1段あたりの遅延量と同一の時間遅延させ、第二のスイッチ回路が活性化されるとき遅延させないで起動信号をインバータ遅延回路に入力する起動信号制御回路とを備える。

(もっと読む)

ラッチ構造及びラッチを用いる自己調整パルス生成器

開示は、ラッチ構造及びラッチを用いる自己調整パルス生成器を含む。実施形態において、システムは、第1のラッチと、第1のラッチにタイミング信号を供給するように連結されたパルス生成器とを含む。パルス生成器は、第1のラッチに整合する特性を持つ第2のラッチを含む。  (もっと読む)

(もっと読む)

負荷駆動回路、遅延回路、および半導体装置

【課題】 プラズマディスプレイにおけるスキャンドライバにおいて、出力端子が短絡した場合に、素子破壊からICを保護する。

【解決手段】 レベルシフト9、IGBT1、2、AND素子10を備え、入力信号IN1、IN2、IN3、PULSE_INを制御することにより、出力DOUTをHi/Lo/HiZ/擬似Hiの4状態に制御する。所定時間後に出力をHiから擬似Hiに遷移させることにより、出力短絡から素子を保護する。また、2組のインバータ回路間に並列接続されたNMOSを有し、NMOSのゲートに2段目のインバータ回路の出力を接続し、NMOSのソースにGND、ドレインに初段のインバータ回路の出力を接続した遅延回路をレベルシフト9のPULSE_INに接続することにより、遅延時間の温度依存性をほとんど無くすことができる。

(もっと読む)

161 - 180 / 420

[ Back to top ]