Fターム[5J001BB12]の内容

Fターム[5J001BB12]に分類される特許

121 - 140 / 420

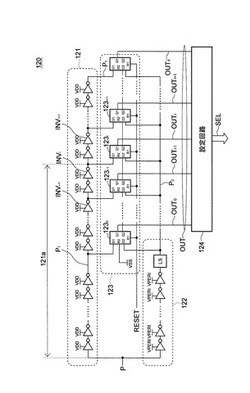

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

遅延回路

【課題】製品ごとのトランジスタの閾値電圧のばらつきに基づく遅延量の変動を抑制することが可能な遅延回路を提供する。

【解決手段】容量素子M5〜M8は、インバータバッファ11〜14のそれぞれの出力端子と接続されている。Vt依存電圧発生部2は、自己の有するMOSトランジスタの閾値電圧Vtnに応じた電圧を、容量素子M5〜M8が有するMOSトランジスタの基板に印加する。

(もっと読む)

DLL回路及びその制御方法

【課題】クロックのパルス幅が狭い場合、及び広い場合において、合成回路の誤動作を回避し、動作周波数の高速化に対応可能とするDLLの提供。

【解決手段】外部クロック(CK)の第1遷移(Rise)に対応して互いに異なる遅延時間の信号を出力し、CKの第2の遷移(Fall)に対応して互いに異なる遅延時間の信号を出力する第1の可変遅延回路20と、第1の可変遅延回路からの信号をそれぞれ受ける第2の可変遅延回路10R、10Fからの出力信号を合成して出力する第1の合成回路30とを備え、第2の可変遅延回路は第1の可変遅延回路からの信号からワンショットパルスを生成するワンショットパルス生成回路と、リセット端子を備えるラッチ回路と、ラッチ回路のセット出力の遷移エッジを受け、所定の比率で合成した信号を出力する第2の合成回路と、を備え、第2の合成回路の出力がラッチ回路のリセット端子に入力される。

(もっと読む)

デューティ可変回路

【課題】低電力、小面積で実現するデューティ可変回路を提供する。

【解決手段】それぞれ一対の相補型のトランジスタを有する第1のCMOSインバータ回路と、第2のCMOSインバータ回路と、前記第1のCMOSインバータ回路と第2のCMOSインバータ回路の間に直列接続され、ゲートがグランドに接続されたPMOSトランジスタと、前記第2のCMOSインバータ回路に接続された第3のインバータ回路と、前記第2のCMOSインバータ回路への電源及びグランドの供給がそれぞれ制御できる第1及び第2のスイッチを有する。前記第3のインバータ回路の出力信号を用いて前記第1、第2のスイッチの開閉を切り替えることによって、前記第2のCMOSインバータ回路の入力信号の論理が遷移する際の前記第2のCMOSインバータ回路の貫通電流を低減する。

(もっと読む)

DLL回路

【課題】高精度な同期特性を有するDLL回路を提供する。

【解決手段】第1クロック信号CLK1が入力され、第1クロック信号CLK1を遅延した第2クロック信号CLK2を出力するとともに、制御信号Vcにより遅延時間が可変される可変遅延回路11と、第1クロック信号CLK1および第2クロック信号CLK2が入力され、第1クロック信号CLK1と第2クロック信号CLK2との位相を比較して、その位相差ΔΦに応じた信号を出力する位相検出回路12と、位相検出回路12の出力V1を積分する積分回路13と、積分回路13の出力V2を予め定めた基準値Vrefと比較し、比較結果を出力する比較回路14と、比較回路14の出力V3を平均化し、高周波成分を除去した信号を、制御信号Vcとして可変遅延回路11に出力するローパスフィルタ15と、を具備する。

(もっと読む)

三分周直交位相周波数分周器

【解決手段】局部発振器は、VCOの出力に結合されたプログラム可能な周波数分周器を備える。周波数分周器は、3で周波数分周するためにセットされることができる。除数に関係なく、周波数分周器は、90度で位相が互いに異なる直交位相信号(I、Q)を出力する。3で分周するために、周波数分周器は、三分周周波数分周器を備える。三分周周波数分周器は、三分周回路、遅延回路、及びフィードバック回路を備える。三分周回路は、VCOから信号を周波数分周し、それから、120度で位相が互いに異なる三つの信号C、A´、及びBを生成する。遅延回路は、信号A´の遅延バージョンAを生成するために、信号A´を遅延する。フィードバック回路は、遅延バージョンA(I)が、信号C(Q)に関して90度位相がずれるように遅延回路を制御する。 (もっと読む)

クロック・データ・リカバリ回路

【課題】

USB2.0規格などの高速シリアル通信に用いるクロック・データ・リカバリ回路に関し、受信データの取り込みエラーを防止し、かつLSI化に適した回路を提供する。

【解決手段】

周期T1のクロックをN分割したT2単位でずらしたN相のクロックを出力する手段6、シリアル転送された信号をT2毎にサンプリングしてT1毎にNビットパラレルデータに変換する手段4、その出力データをデジタル処理してNビットパラレルデータに変換する手段で、またデータ変化点を示すNビットパラレルデータに変換する手段8、変化点を示すデータを位相情報入力として前記デジタル処理されたデータのデータ変化点の略中間位置を示すデータを出力する手段10、その出力データが示したビット位置に対応する前記デジタル処理されたデータを復元データとする手段12を備える。前記デジタル処理は、移動平均処理、デューティずれ補正処理とすることができる。

(もっと読む)

DLL回路

【課題】広い周波数帯域で動作するDLL回路を提供する。

【解決手段】入力クロック信号CLKの周波数を検出する周波数検出回路12が設けられ、当該検出結果に応じたデータはレジスタ13に格納される。レジスタ13は当該検出結果に応じたモード切替信号MODEをVCDL回路11に出力する。入力クロック信号CLKの周波数が所定値より小さい場合は、各遅延素子の遅延量が大きくなり、入力クロック信号CLKの周波数が所定値以上の場合は、各遅延素子の遅延量が小さくなるように構成されている。具体的には、VCDL回路11において、各遅延素子の出力端子にスイッチと容量素子を付加し、モード切替信号MODEに応じてスイッチをオン・オフさせることで、容量素子を各遅延素子の出力端子に接続するか否かを切り替えるという構成が採用されている。

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

ヒステリシスコンパレータ回路及びそれを用いた遅延回路

【課題】回路規模を大型化することなく、大きな遅延時間を得る。

【解決手段】遅延対象の矩形波の入力信号Vinを台形波発生回路10により台形波信号Vcに変換し、その台形波信号の中間電圧よりも高く設定された第1のスレッショルド電圧Th1を有するインバータ21と、中間電圧よりも低く設定された第2のスレッショルド電圧Th2を有するインバータ22とで、台形波信号Vcと第1及び第2のスレッショルド電圧を比較し、インバータ21とインバータ22の出力でバッファ回路23を駆動し、台形波信号Vcに同期して反転し、かつ遅延した矩形波の出力信号Voutを生成する。

(もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

多相クロック生成回路、オーバーサンプリング回路及び位相シフト回路

【課題】より位相差の微小な多相クロックを生成しつつ、消費電流の増大を抑制した多相クロック生成回路及びオーバーサンプリング回路を提供する。

【解決手段】1対の入出力端子と、遅延量制御端子にバイアスした電圧に応じた遅延量を発生させる2つの遅延ラインの出力の位相差を検出する位相比較器13と、位相比較器13の出力を平均化する平均化フィルタ14とを備え、一方の遅延量制御端子に基準電圧を接続し、他方の遅延量制御端子に平均化フィルタ14の出力を接続し各遅延ラインの出力が所定の位相差を持つように制御する遅延量制御部11と、複数かつ同数個の遅延素子を直列に接続した複数の遅延ライン21を備え、各遅延ライン21は基準電圧を接続した遅延素子22の数及び平均化フィルタ14の出力電圧を接続した遅延素子の数の組み合わせを異ならせたクロック遅延部20とを備え、所定の位相差を持つ多相クロックを生成する。

(もっと読む)

半導体集積回路装置

【課題】PLL回路におけるジッタを低減しながら、ワイドレンジで安定した動作を行う。

【解決手段】PLL回路のオシレータを構成する遅延バッファ7のインバータ13,14は、電流制限用トランジスタであるトランジスタ8を介して電源電流が供給されている。トランジスタ8は、バイアス電流である入力信号in1に応じてインバータ13,14に供給する電流制限する。このトランジスタ8を設けたことにより、発振周波数の低い帯域における該インバータ13,14に流れるリーク電流を防止することができる。

(もっと読む)

デジタルDLL回路及び半導体装置

【課題】出力信号のジッターを低減可能としたデジタルDLL回路を提供する。

【解決手段】クロック信号CLKを1周期遅延させるための固定遅延素子の段数を選択する位相判定部1と、位相判定部1で選択した固定遅延素子の段数に基づいて、入力信号INを任意の位相量だけ遅延させて出力する固定遅延素子の段数を選択する位相調整部21とを備えたデジタルDLL回路において、位相調整部21は、選択信号に基づいて、複数段の固定遅延素子と、該固定遅延素子の1段当たりの遅延時間を1/2n刻みで調整する可変遅延部とで生成する遅延時間で、入力信号INを任意の位相量遅延させた出力信号OUTを生成する。

(もっと読む)

クロック信号生成装置および離散時間型回路

【課題】電源電圧、環境温度などの外部変動要因により、離散時間型回路において必要となるクロック信号に変動が生じた場合などにおいて、離散時間型回路が必要とするノンオーバーラップ時間、およびクロック信号のデューティ比を最適に設定することができるクロック信号生成装置を提供すること。

【解決手段】本発明のクロック信号生成装置において、クロック信号遅延算出部は、クロック信号生成回路の可変遅延回路における外部変動要因による遅延特性をモニターする遅延検出回路を有して、N相のクロック信号の遅延量を算出し、クロック信号遅延制御部は、遅延変動データ部に記憶されている外部変動要因をパラメータとした遅延変動データと、算出されたN相のクロック信号の遅延量とに基づいて、可変遅延回路における遅延量を可変するよう構成されている。

(もっと読む)

デューティ補正回路

【課題】プロセスバラツキや、プロセス変更によりN型トランジスタ及びP型トランジスタ双方の特性が設計段階に対してずれても、デューティ比を所望の数値に補正するデューティ補正回路を提供する。

【解決手段】本発明のデューティ補正回路は、第1電源及び第1出力間に設けられ、第1信号をゲートに受ける第1チャネル型第1MOSトランジスタ(以下Tr)と、第2の電源及び第1出力間に設けられ、第1信号をゲートに受ける第2チャネル型第2MOSTrと、第1電源及び第1出力間に第1MOSTrと直列に設けられた第1チャネル型第3MOSTrと、第1電源及び第2の出力間に設けられ、第1出力線がゲートに接続された第1チャネル型第4MOSTrと、第2電源及び第2出力間に設けられ、第1出力線がゲートに接続された第2チャネル型第5MOSTrと、第1電源及び第2出力間で第4MOSTrと直列に設けられた第1チャネル型第6MOSTrと、第3及び第6MOSTrのゲートに其々バイアス電圧を印加するバイアス回路を備える。

(もっと読む)

デューティサイクル補正回路及び方法

【課題】本発明は、より安定しているデューティサイクル補正動作を具現するデューティサイクル補正回路及び方法を提供する。

【解決手段】本発明は、デューティ比感知信号に応じて、複数ビットのプルアップ制御信号及び複数ビットのプルダウン制御信号の論理値を交互に変化させるデューティ比制御手段と、複数ビットのプルアップ制御信号及び複数ビットのプルダウン制御信号に応じて、第1のドライバ及び第2のドライバの駆動力を調節して、補正クロックを出力するデューティ比補正手段と、補正クロックのデューティ比を感知して、デューティ比感知信号を生成するデューティ比感知手段とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

DLL回路

【課題】補間回路の最小動作周期を低減でき、DLLの最大動作周波数を向上させることができる、DLL回路を提供する。

【解決手段】位相検知回路21は、入力される基準クロック信号とレプリカ回路17から出力されるクロック信号との位相の差を検知し遅延制御回路22に出力する。遅延制御回路22は、位差の信号を基に、基準クロック信号の位相を調整する制御信号を出力する。そして、遅延制御回路22から出力される制御信号を基に、マルチプレクサ12、13は、粗調整遅延回路10からインバータ2段分の遅延差を有する信号を選択して出力し、第1の微調整遅延回路14は、マルチプレクサから入力した2段分の遅延差の信号を基に、インバータ1段分の遅延差を有する信号を出力する。第2の微調整遅延回路15は、この1段分の遅延差を有する信号に基づいてクロック信号の位相を調整する。

(もっと読む)

121 - 140 / 420

[ Back to top ]