Fターム[5J001BB12]の内容

Fターム[5J001BB12]に分類される特許

41 - 60 / 420

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

内部クロック調整回路

【課題】半導体記憶装置の動作テストに際し、ストローブ信号の発生タイミングを適切に設定する。

【解決手段】遅延回路132は、外部クロック信号CLKTを遅延させることにより内部クロック信号DCLKを出力する。位相差判定回路144に含まれる検出電位発生回路は、内部クロック信号RDCLKTのアクティブエッジのタイミングと、目標となる外部クロック信号CLKTのタイミングとの差分に対応する検出電位を第1ノードに発生させる。位相差判定回路144に含まれる基準電位発生回路は、基準電位を第2ノードに発生させる。位相制御回路134は、検出電位にしたがって内部クロック信号DCLKを遅延させる。このとき、検出電位が基準電位よりも大きいときには内部クロック信号DCLKの1回あたりの調整量が変化する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

半導体装置

【課題】回路を通常の動作していない状態からスタンバイ状態に変える、及び、回路全体は通常の動作をしていない状態だがバイアス条件を変える、という具合に条件を変化させることでストレスを緩和する。

【解決手段】スタンバイ制御信号が活性状態のとき、前記タイマー回路からのタイマー出力信号に基づき、機能回路部30の論理状態を所定時間毎に変えるMODE制御信号を生成するモード制御回路20と、機能回路部30の出力信号を受け前記出力信号の出力を制御する出力制御回路50と、を備え、出力制御回路50はMODE制御信号をDelay回路40で遅延させて生成されるDelay出力信号に基づき、機能回路部30がMODE制御信号により論理状態を変えている間、前記機能回路部出力信号を出力に伝達せずに、機能回路部30がMODE制御信号によって前記論理状態を変える直前の機能回路部出力信号を保持出力する。

(もっと読む)

信号伝送回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】伝送される信号の論理を保ち、かつ、デューティ崩れの蓄積、加算を解消することが可能な信号伝送回路、カラムA/D変換器、固体撮像素子およびカメラシステムを提供する。

【解決手段】主信号が伝送される主伝送ライン11と、主伝送ライン11に縦続接続されるように配置され、伝搬される信号の反転機能を有する複数のリピータ13−1〜13−xと、各リピータの出力側の主伝送ラインから分岐するように接続された副伝送ライン14−1〜14−xと、各副伝送ラインに接続され、信号が供給される下位回路16−1〜16−xと、を有し、副伝送ラインが、主信号の反転論理の信号がリピータから供給される副伝送ラインである場合には、その副伝送ラインに反転回路15が配置されている。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

半導体装置

【課題】広い変動幅で入力信号を遅延させる一方、入力端に加えられるローディング及びその動作電流量を最小限に維持することができる遅延ラインを備える半導体装置を提供すること。

【解決手段】遅延制御コードONC_PUBに応じて、入力信号を遅延して第1の遅延入力信号及び第2の遅延入力信号を出力する共通遅延部200と、遅延制御コードCON_1に応じて、第1の遅延入力信号を遅延して第1の出力信号を出力する第1の遅延部220と、遅延制御コードCON_2に応じて、第2の遅延入力信号を遅延して第2の出力信号を出力する第2の遅延部240とを備え、共通遅延部から伝達される第1の遅延入力信号が第1の遅延部中を通過する長さである第1の遅延経路と、共通遅延部から伝達される第2の遅延入力信号が第2の遅延部中を通過する長さである第2の遅延経路とに、所定の長さの差があることを特徴とする。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

遅延回路、及び電子機器

【課題】遅延回路のキャパシタの容量を増大させることなく、外来ノイズの影響による出力電圧の誤動作を防止する。

【解決手段】キャパシタと第1のノードを介して接続され、前記キャパシタを充電または放電する定電流源と、入力電圧が第1のレベルに変化したときに前記キャパシタを放電または充電し、入力電圧が第2のレベルに変化したときに前記キャパシタを充電または放電する充放電回路と、前記キャパシタの充放電の開始から、前記第1のノードの電圧が所定の検知電圧を超えるまでの時間遅延して、出力電圧のレベルを第1のレベルから第2のレベルに変化させる電圧検知回路とを有する遅延回路において、前記入力電圧が第2のレベルであって、かつ前記出力電圧が第2のレベルに変化したときに、前記第1のノードの電圧を前記検知電圧を超えるレベルに保持する電圧保持回路を備えることで出力電圧の誤動作を防止する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

遅延固定ループ及びその駆動方法

【課題】遅延固定にかかる時間を短縮し、遅延固定のための回路の電流消費を低減する遅延固定ループを提供すること。

【解決手段】特定パルス幅を有する遅延パルス(DPULSE)を生成する遅延パルス生成部(210)と、遅延パルスをコード化してコード値(CODE)を出力するコード化部(220)と、入力クロック(CLK)をコード値に該当する分だけ遅延させ、遅延された固定クロック(DLLCLK)を生成する遅延ライン(230)とを備える。遅延パルスが、入力クロックの整数倍に該当する第1の期間と特定レプリカ遅延期間である第2の期間との差に該当する第3の期間の間、ロジックハイレベル状態を有することを特徴とする。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

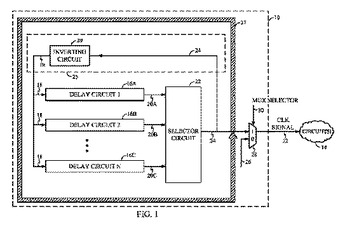

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 起動時に遅延回路部の遅延時間を調整する半導体装置を提供する。

【解決手段】 半導体装置は、電源立ち上げ動作時に遅延回路部の遅延時間を検出し、検出結果に基づいて遅延調整信号を生成する遅延制御部と、遅延回路部に設けられ、遅延調整信号に応じて遅延回路部の遅延時間を調整する遅延調整部とを備える。

(もっと読む)

半導体装置、半導体装置の制御方法及び該半導体装置を用いたシステム

【課題】電源電位変動に対する第1の遅延変動量を有するアナログ回路と、第1の遅延変動量より小さな第2の遅延変動量を有するデジタル回路とを備える半導体装置において、電源電位の変動に伴うアナログ回路とデジタル回路との間での遅延量のミスマッチを解消する。

【解決手段】アナログ回路は第1の電源電位に接続されている場合に、デジタル回路として、第1の電源電位に接続された第1の回路部分において発生した遅延量である第1の遅延量を検出する検出回路と、第1の電源電位よりも電位変動量が小さい第2の電源電位に接続され、アナログ回路を制御する制御信号を生成する第2の回路部分と、を設ける。第1の遅延量に相関させて第2の回路部分における遅延量である第2の遅延量を制御する。

(もっと読む)

半導体装置、および該半導体装置における遅延回路の遅延コード自動設定方法

【課題】入力されるデータ信号のセットアップ及びホールド時間を調整する遅延回路における最適な遅延時間(遅延コード)を、半導体装置の実際の動作条件下において自動的に設定する。

【解決手段】パッド11から、ターゲットとなるデータ信号ADD/CMDを遅延回路13に入力し、遅延回路13の遅延コードCODET<2:0>を変えて、遅延回路から出力される遅延信号の遅延時間を変化させる。そして、この遅延された信号をラッチ回路14によりラッチし、遅延された信号PA0DBとラッチされたデータ信号PA2Bとの一致または不一致を判定し、一致すると判定した場合に、この判定結果に基いて遅延コードCODET<2:0>を決定し、決定後の遅延コードにより遅延回路13を動作させる。

(もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

41 - 60 / 420

[ Back to top ]