Fターム[5J001BB12]の内容

Fターム[5J001BB12]に分類される特許

61 - 80 / 420

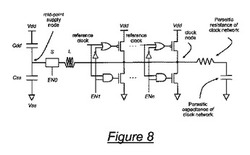

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

ノイズ除去装置

【課題】使用環境状況の影響を受けずに、ノイズを確実に除去する。

【解決手段】n個のD型フリップフロップを直列に接続し、各D型フリップフロップの出力した信号の論理積を出力とするデジタル・フィルタ20と、m×2個のプリミティブ素子を有するインバータを直列に接続したディレイ・フィルタ30を並列に接続する。入力信号INPUTを両フィルタに入力し、AND回路40が各フィルタの出力する信号DELAYと信号ANDの論理積である信号FILTを出力する。発生期間がクロック信号の周期とDFF回路の段数に対応する期間より短いノイズをデジタル・フィルタ20が除去し、インバータ回路の遅延時間より周期の短いノイズをディレイ・フィルタ30が除去する。

(もっと読む)

遅延発生装置および半導体試験装置

【課題】差動ペアトランジスタを用いない比較器を備えた遅延発生装置およびこの遅延発生装置を備えた半導体試験装置を提供することを目的とする。

【解決手段】入力信号に対して設定された時間だけ遅延を持たせるための静電容量を有する遅延部111と比較基準電圧を生成するためのDAコンバータ110と遅延部から出力される出力電圧と比較基準電圧とを比較する比較器1とを備える遅延発生装置であって、比較器1は、比較基準電圧Vthに基づく閾値と出力電圧とを比較して反転するインバータ回路2Aと、インバータ回路2Aの正側電位Vd1を設定する第1の電圧源5と、インバータ回路2Aの負側電位Vs1を設定する第2の電圧源6と、を備えている。

(もっと読む)

半導体装置及びその制御方法並びにデータ処理システム

【課題】レベルシフトによって生じるスキューを無くす。

【解決手段】電圧の振幅値がVPERIである内部クロック信号LCLK3を電圧の振幅値がVDDである内部クロック信号LCLK4に変換するレベルシフト回路200aと、電圧の振幅値がVPERIである内部データ信号BD,BEを電圧の振幅値がVDDである内部データ信号CD,CEに変換するレベルシフト回路200bと、内部クロック信号LCLK4に基づいて相補の内部クロック信号LCLK5,LCLK5Bを生成するクロック分割回路300と、内部データ信号CD,CEに基づいて、内部クロック信号LCLK5,LCLK5Bにそれぞれ同期してデータ出力端子14から連続的に出力する出力回路400と、を備える。本発明によれば、出力回路400に入力される前にレベルシフトを行っていることから、出力データ間にスキューが生じない。

(もっと読む)

遅延回路及び遅延回路を備えた半導体記憶装置

【課題】トランジスタ特性のバラツキに応じて遅延回路の遅延特性を設定することを特徴とする。

【解決手段】定電流源12と、ゲートとドレインが結合され、定電流源の電流が流れるMOSトランジスタ14とを含み、MOSトランジスタ14のゲートのノードからバイアス電圧を出力するバイアス回路部10と、インバータ26と、電流通路がインバータの入力ノードと基準電位ノードとの間に直列に挿入され、バイアス電圧がゲートに供給されるMOSトランジスタ21及び入力信号INがゲートに供給されるMOSトランジスタ22と、インバータの入力ノードと基準電位のノードとの間に挿入された容量25と、電流通路が電源電位ノードとインバータの入力ノードとの間に挿入され、入力信号がゲートに供給されるMOSトランジスタ23とを含み、インバータの出力ノードから信号を出力する遅延部20とを具備している。

(もっと読む)

遅延ロックループ回路、半導体集積回路装置

【課題】低い周波数から高い周波数までの幅広い周波数帯域に対応して、回路面積の小さい遅延ロックループ回路、その遅延ロックループ回路を搭載する半導体集積回路装置を提供する。

【解決手段】遅延ロックループ回路は、位相変更回路と、遅延線回路と、遅延制御回路とを具備する。位相変更回路は、入力される基準クロックに対して第1の位相差を有する第1の信号と、第2の位相差を有する第2の信号とを出力する。第1の位相差と第2の位相差との差分は所定の位相遅延量を示す。遅延線回路は、変更可能な単位遅延量を備える遅延回路を複数含む。遅延制御回路は、単位遅延量の合計が基準位相遅延量になるように単位遅延量を制御する。

(もっと読む)

遅延回路

【課題】 遅延時間の電源電圧依存性を低減することのできる遅延回路を提供する。

【解決手段】 ソースドレイン電極端が信号線S−midと第1のノード11との間に接続されフロントゲート及びバックゲートが第1及び第2の電源ラインにそれぞれ接続された第1のMOSトランジスタTP12と、前記第1のノードと前記第1の電源ラインとの間に接続された第1の容量素子Cs11と、第1出力端に一方又は他方の論理レベルを持つ選択信号SEL1、SEL2を出力する遅延制御部DC1と、前記第1のノードと前記遅延制御部の第1出力端との間に接続された第1の複数の容量素子Cv11、Cv12を含む遅延回路。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

データ受信回路

【課題】データ信号の立ち上がりエッジと立ち下がりエッジとの間の定常的な遅延の差を小さくする。

【解決手段】データ受信回路であって、データを伝送するデータ信号を増幅して出力する増幅回路と、第1の制御信号に従って前記増幅回路の出力を遅延させ、第1の遅延データ信号として出力する第1の遅延回路と、第2の制御信号に従って前記増幅回路の出力を遅延させ、第2の遅延データ信号として出力する第2の遅延回路とを有する。

(もっと読む)

遅延装置

【課題】精度良く信号を遅延する。

【解決手段】遅延対象信号を遅延した遅延信号を出力する遅延装置であって、遅延対象信号を遅延させた信号を出力する遅延回路と、少なくとも一部の期間において遅延対象信号とは異なる論理値の信号を遅延回路へと入力させて、遅延回路に入力される信号の論理値毎の割合を基準割合に近付ける調整部と、を備え、調整部は、遅延対象信号および遅延対象信号を論理反転した反転信号を切り替えて遅延回路へと入力させる、遅延装置を提供する。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

遅延ライン

【課題】半導体装置に備えられ、入力信号を遅延させる遅延ラインを提供すること。

【解決手段】第1の遅延制御コードFIR_DCON<0:5>に応じて入力信号INPUT_SIGの遅延量を調整する遅延量調整部300と、第2の遅延制御コードSEC_DCON<0:5>に応じて第1の変動幅で変動する第1の遅延ブロック322<0:4>の個数と、その遅延量が第2の変動幅で変動する第2の遅延ブロック324<0:4>の個数とを決定する遅延部320とを備え、前記第1の変動幅の遅延量と第2の変動幅の遅延量とは、前記遅延量調整部300によって決定され、前記第1の変動幅および第2の変動幅の電源電圧のレベル変動に対応することを特徴とする。

(もっと読む)

可変遅延回路、及びスペクトル拡散回路

【課題】従来技術と比較して、簡易な構成でスペクトラム拡散機能を有する可変遅延回路及びスペクトル拡散回路を提供する。

【解決手段】第1の直列回路の遅延セル14の各々及び第2の直列回路の遅延セル14の各々に対応して設けられると共に、対応する遅延セル14から出力されたクロック信号が入力され、かつ切換信号が入力され、入力されたクロック信号に同期させて入力された切換信号を保持し、保持した切換信号を選択信号として対応する遅延セルに出力し、かつ保持した切換信号を出力するフリップフロップ28が直列接続された第3の直列回路と、入力されたクロック信号に同期させて入力された切換信号を保持し、保持した切換信号を出力するフリップフロップ28と、第3の直列回路の最後段に設けられたフリップフロップ28から出力された切換信号を反転して、第1の直列回路の最前段に設けられた遅延セル14に入力するインバータ30とを含む。

(もっと読む)

レベルシフト回路

【課題】デューティ比を維持したレベルシフト回路を提供する。

【解決手段】低電圧系電源電圧Vdd1と接地電位GNDを振幅とする入力信号を受け、高電圧系電源電圧Vdd2と接地電位の間の振幅に変換した出力信号電圧Voutを出力するレベルシフト電圧生成回路201と、レベルシフト電圧生成回路のレプリカ構成とされ、低電圧系の閾値電圧と高電圧系の閾値電圧を監視し、入力電圧を低電圧系の論理閾値に、出力電圧を高電圧系の論理閾値として、入力電圧が低電圧系の論理閾値を横切るとき、出力電圧が高電圧系の論理閾値を横切るように同期した出力電圧を生成させるレプリカ回路202と、レベルシフト電圧生成回路の出力電圧とレプリカ回路の出力電圧の変動を調整するためのバイアスを生成し、前記レベルシフト電圧生成回路と前記レプリカ回路に供給するバイアス生成回路203と、を有する。

(もっと読む)

差動受信回路

【課題】差動対を備える差動受信回路であって、出力するデータの立ち上がりと立ち下がりの変化タイミングの遅延差を低減した差動受信回路の実現。

【解決手段】差動対を備え、入力される相補入力信号inp,innを増幅して相補出力信号A,Bを出力する差動アンプ回路1と、直列に接続された2個以上のインバータInvA1,InvA2,InvA3を備え、初段に差動アンプ回路の出力する相補出力信号の一方Aが入力される第1のインバータラインと、差動アンプ回路の出力する相補出力信号の一方Bが入力される少なくとも1個のインバータInvB1,InvB2を備え、2個以上のインバータを備える場合には直列に接続され、初段に相補出力信号の一方が入力される第2のインバータラインと、を備え、第1のインバータラインおよび第2のインバータラインの初段からの段数が1段異なる1組の2個のインバータの出力を接続した。

(もっと読む)

半導体集積回路

【課題】論理ゲートを構成するトランジスタの特性劣化を抑制する。

【解決手段】半導体集積回路70には、マルチプレクサ1、信号発生回路2、制御回路3、m個のインバータINV1乃至m列、n個の2入力NOR回路NOR1乃至n、縦続接続されるn個の2シフトレジスタSR1乃至nが設けられる。制御回路3は、クロック信号が供給される通常動作ときにディセーブル状態の制御信号Sctを生成し、クロック信号が供給されない通常動作以外のときにイネーブル状態の制御信号Sctを生成する。マルチプレクサ1は、クロック信号Sclkと信号発生器2から出力される低周波信号Ssgが入力され、制御信号Sctがディセーブル状態の時インバータINV1乃至m列にクロック信号Sclkを供給し、制御信号Sctがイネーブル状態の時インバータINV1乃至m列に低周波信号Ssgを供給する。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

半導体集積回路装置

【課題】小さい面積で十分な遅延時間を確保する。

【解決手段】 入力に基づいて充電点に充電を行う第1のトランジスタと前記入力に基づいて放電点から放電を行う第2のトランジスタとにより構成される第1のインバータ(PT21,NT21)と、前記充電点と前記放電点との間に、ドレイン・ソース路が並列に設けられたP型の第3のトランジスタ及びN型の第4のトランジスタ(PT22,NT22)と、前記充電点又は前記放電点の電位を反転させて前記第3及び第4のトランジスタのゲートに供給して、前記充電点又は前記放電点から前記入力の遅延信号を得る第2のインバータ(INV21)とを具備したことを特徴とする。

(もっと読む)

遅延信号生成回路、及び、遅延回路

【課題】入力された信号に所定の遅延時間を安定的に挿入し得る遅延信号生成回路及び遅延回路を提供する。

【解決手段】遅延信号生成回路は、供給される電源の電圧によって、その遅延時間が変化する、1又は複数の第1遅延回路と、前記第1遅延回路と同一の回路構成を有しており、供給される電源の電圧によって、その遅延時間が変化する第2遅延回路と、前記第1遅延回路と前記第2遅延回路に電源を供給する、制御電源回路とを有する、電源供給回路と、を備えるとともに、前記制御電源回路は、入力クロック信号と遅延クロック信号との間の位相差を検出し、前記位相差に基づいて、前記入力クロック信号と前記遅延クロック信号との間の位相差が解消されるように、前記第1遅延回路と前記第2遅延回路に供給する電源の電圧を制御する。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

61 - 80 / 420

[ Back to top ]