Fターム[5J022CB06]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 加減算制御 (575)

Fターム[5J022CB06]の下位に属するFターム

基準電圧切換動作制御 (53)

Fターム[5J022CB06]に分類される特許

161 - 180 / 522

アナログ信号をデジタル信号に変換する集積回路、システム、及び、AD変換方法

【課題】アナログ信号をデジタル信号に変換する集積回路、システム、及び、操作方法を提供する。

【解決手段】アナログ信号を少なくとも一つのデジタル信号に変換することができる集積回路として、本集積回路は、第一アナログ信号を受信することができる第一入力端と、第一アナログ信号を量子化して、第一組2n-1個のデジタル値を出力することができる第一組の2n-1インバータ(第一組2n-1個のデジタル値はそれぞれ0か1)と、第一組2n-1個のインバータと接続され、第一組2n-1個のデジタル値を加算して、少なくとも一つのデジタル信号に対応する第一整数値を出力する第1の一加算器とを備える。

(もっと読む)

アナログデジタル変換回路及び光結合型絶縁回路

【課題】演算増幅器のオフセット電圧を低減し、かつ容量雑音を低減して小型化可能としたアナログデジタル変換回路及び光結合型絶縁回路を提供する。

【解決手段】アナログ信号を入力し、第1の期間は前記アナログ信号を逆相で出力し、第2の期間は正相で出力する第1のスイッチ回路と、前記アナログ信号をクロスカップルに入力して積分するスイッチトキャパシタ型の第1の積分回路と、前記第1の積分回路の出力及び同相出力電位を出力する第2のスイッチ回路と、前記第2のスイッチ回路の出力をサンプリング及び積分する第2の積分回路と、前記第2の積分回路の出力を1ビット出力する量子化回路と、前記量子化回路の出力をアナログ信号とするデジタルアナログ変換回路と、を備え、前記第1及び第2の積分回路は、前記デジタルアナログ変換回路の出力をそれぞれクロスカップルに入力して積分する。

(もっと読む)

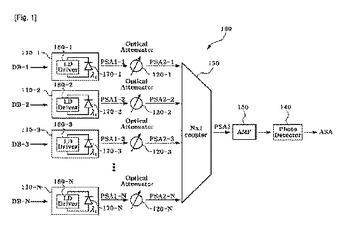

デジタル−アナログ変換器

デジタル−アナログ変換器(DAC)は、複数の入力信号に応答して複数の第1の光信号を生成するための複数の電光変換器と、第1の光信号の強度を減衰させ、複数の第2の光信号を生成するための複数の光減衰器と、第2の光信号を組み合わせ、第3の光信号を生成するための光学カプラと、第3の光信号を電気的アナログ信号に変換するための光検出器とを含む。  (もっと読む)

(もっと読む)

A/D変換誤差抑圧制御装置及びA/D変換誤差抑圧制御方法並びにプログラム

【課題】光アンプ装置に対する入力光信号および出力光信号の一部をA/D変換器を用いてA/D変換し、その変換結果を利用して光アンプ装置を制御する際、A/D変換器のA/D変換誤差を抑圧できるようにする。

【解決手段】A/D変換誤差判定回路80は、A/D変換器51、52に想定されるA/D変換誤差の最大誤差と、入出力光信号モニタ値と、設計利得値とに基づいて、入力光信号90のレベルが変動している状態なのか、それともA/D変換器51にA/D変換誤差が発生している状態なのかを判定する。A/D変換誤差が発生している状態であれば、制御回路70aは、入力光信号モニタ値の中心値(平均値や中央値)と入力光信号モニタ値とからA/D変換誤差の値を算出し、設計利得値をA/D変換誤差分補正することにより、目標利得値を算出する。そして、入力光信号モニタ値が目標利得値となるように、光アンプ装置を制御する。

(もっと読む)

DA変換回路

【課題】DA変換回路の変換周期を広げることなく変換分解能を上げるとともに、回路構成の複雑化を抑制すること。

【解決手段】PWM回路11は、ディジタル入力値Dinの上位N(Nは正の整数)ビット分Xに基づいてパルス幅変調されたパルス幅変調パルスP(A)を生成し、重畳部20は、ディジタル入力値Dinの下位m(mは正の整数)ビット分Zに対応した数の1クロック分の単位パルスUを、ディジタル入力値Dinの上位Nビット分に対応した変換周期Tの最終の1クロック分に分散させて重畳させる。

(もっと読む)

変換装置並びに信号発生装置及び信号測定装置

【課題】入出力特性が互いに異なる複数の変換器の入出力特性を合致させることが可能な変換装置、及び当該変換装置を備える信号発生装置及び信号測定装置を提供する。

【解決手段】変換装置1は、入出力特性が互いに異なる複数のA/D変換器10a〜10nと、A/D変換器10a〜10nに共通する入出力特性を示す理想直線が設定されており、A/D変換器10a〜10nの全ての入出力特性が理想直線に合致するようにA/D変換器10a〜10nの各々から出力されるディジタル信号を補正する補正部20とを備える。

(もっと読む)

A/D変換回路、電子機器及びA/D変換方法

【課題】A/D変換の特性を改善できるA/D変換回路、A/D変換方法等の提供。

【解決手段】A/D変換回路は、比較回路10と、逐次比較レジスタSARを有する制御回路20と、制御回路20からの逐次比較用データをD/A変換する第1のD/A変換回路DAC1と、時間的に変化するコードデータをD/A変換する第2のD/A変換回路DAC2を含む。比較回路10は、入力信号のサンプリング信号とコード信号の加算信号と、D/A出力信号とを比較する処理、或いはサンプリング信号と、D/A出力信号とコード信号の加算信号とを比較する処理を行い、制御回路20は、逐次比較結果データとコードデータとに基づき求められる出力データを入力信号のA/D変換データとして出力する。

(もっと読む)

画像形成装置及びその制御方法

【課題】複数のCPUを用いた分散制御において、コスト増加を招くことなく、各CPUにおける基準電位の差による各A/D変換器の誤差を低減する画像形成装置を提供する。

【解決手段】本画像形成装置は、複数のCPUを用いた分散制御を実現する。また、本画像形成装置は、補正モードにおいて、同一の表面電位計からの出力が各A/D変換器対して入力されるようにスイッチを制御した状態で、各A/D変換器から出力されるデジタルデータの差分を算出する。さらに、本画像形成装置は、通常測定モードにおいて、補正モードで算出された上記差分を解消するように、各A/D変換器からの出力を補正する。

(もっと読む)

A/D変換回路、信号処理回路、及びブレ検出装置

【課題】相関性のある複数のアナログ信号を精度良くA/D変換することができるA/D変換回路、信号処理回路、及びブレ検出装置を提供する。

【解決手段】切替部1,2は、同一期間に入力されたVA信号及びVB信号のそれぞれの出力先を、A/D変換部3,4のサンプリング周期毎に、A/D変換部3,4のそれぞれへ交互に切り替える。A/D変換部3,4は、切替部1,2から出力されたVA信号及びVB信号をA/D変換し、デジタル信号を生成する。演算部7は、VA信号が入力されたA/D変換部3,4のそれぞれから出力されたデジタル信号の加算演算の結果と、VB信号が入力されたA/D変換部3,4のそれぞれから出力されたデジタル信号の加算演算の結果との差動演算又は除算演算を行う。

(もっと読む)

温度とデジタルコード間の線形関係の提供

【課題】 温度とデジタルコード間の線形関係を提供する。

【解決手段】 温度に対応した第1電圧を提供するステップと、入力となる複数のデジタルコードを有する第2電圧を提供するステップと、前記第1電圧と前記第2電圧を用いて、前記温度に対応したデジタルコードを識別するステップとを含み、複数の前記温度は、前記複数のデジタルコードに実質的に線形的に関連する方法。

(もっと読む)

A/D変換方法及び装置

【課題】パルス遅延回路を用いてアナログ入力信号をA/D変換する装置において、変換式を用いることなく、入出力特性を理想特性(直線)に設定できるようにする。

【解決手段】A/D変換装置は、パルス遅延回路と符号化回路とで構成された第1、第2A/D変換部16、26と、アナログ入力信号Vinにオフセット電圧Voffを加えた第1電圧(Voff+Vin)を生成する加算回路14とを備える。第1A/D変換部16には、動作用の電源電圧として第1電圧を印加し、第2A/D変換部26には、動作用の電源電圧として第2電圧(2・Voff−第1電圧=Voff−Vin)を印加する。各A/D変換部16、26からは、第1、第2電源電圧に対応するデータDT1,DT2が出力されることから、減算器6にてその差(DT1−DT2)を求めることで、アナログ入力信号Vinに対応したA/D変換データDT0を生成する。

(もっと読む)

AD変換器

【課題】増幅器の出力抵抗R1の抵抗値と平均化用抵抗素子Raveの抵抗値との関係に制限されることなく、オーバーレンジ範囲を最小限にとどめて低電力で小面積なAD変換器を提供する。

【解決手段】第1電圧と第2電圧との間を分圧して複数の基準電圧を生成する基準電圧発生器と、各基準電圧と入力信号の電圧との差電圧を増幅する複数の増幅器と、増幅器の出力端子間を接続する複数の平均化用抵抗素子とを備え、さらに、第1電圧よりも高い第3電圧と入力信号の電圧との差電圧を増幅する第1増幅器と、複数の増幅器のうち第1電圧が基準電圧として入力された増幅器の出力端子と第1増幅器の出力端子とを接続する第1抵抗素子とを有する第1平均化補助回路を複数設ける。

(もっと読む)

パイプライン型A/D変換器

【課題】パイプラインステージの入出力特性の誤差を補正し、ステージ出力をデコードしたときの折り返しの発生を防止して、出力レンジを有効に使う。

【解決手段】複数ステージP11〜P1nにより順次、入力アナログ信号から部分デジタルデータを生成し、タイミング調整後デコーダ部3により加算する。各ステージは、部分A/D変換器と、部分D/A変換器と、前段からのアナログ信号に対して部分D/A変換器の出力の加減算を行なう加算器と、加算器の出力を増幅して次段へ供給するゲインアンプとを備える。デコーダ部の出力に後述する補正値を加算する補正値加算部4と、補正値加算部の出力に基づき、ステージの入出力特性の2点における、出力データ間の中点と理想中点との間の誤差を算出し補正値として保持し、補正値加算部に出力する補正値演算部5と、それらを制御して誤差を算出する補正動作を行わせる制御部6とを備える。

(もっと読む)

CV変換回路

【課題】コストおよび消費電力の増大をともなう高速の演算増幅器に依存することなく、IC化に適した回路でもって、高い周波数領域での静電容量挙動を高感度かつ高確度に検出できるようにし、これにより、高周波領域での誘電率挙動による物性の検査や分析を的確に行うことを可能にする。

【解決手段】2つのセンサ容量素子Cx1,Cx2を高周波クロック信号+Φ1に同期して相補的に充放電させる通電回路50と、その2つのセンサ容量素子の通電電流差分ΔIxと上記高周波クロック信号+Φ1とのアナログ乗算操作によって、上記通電電流差分に応じた直流成分を有する電圧Vo1を出力する同期検波回路10と、この同期検波回路10の検波出力電圧を平滑処理しながら増幅する演算増幅器30とを備え、この演算増幅器30の出力から上記2つのセンサ容量素子の静電容量差分ΔCxに対応する直流出力電圧を得る。

(もっと読む)

画像処理装置、サンプリング位置調整方法、および、A/D変換装置

【課題】ダミーデータを生成するための回路を内蔵していないA/Dコンバーターとのシステムにおいて、制御基板における画素単位のデータのサンプリング位置を適切に設定するための技術を提供する。

【解決手段】入力されたアナログ画素データをデジタル画素データに変換して出力するA/D変換部230と、イメージセンサー100から供給されるアナログ画素データの信号として有効な電圧範囲を、A/D変換部230の入力範囲と適合させるオフセット部210と、A/D変換部230から出力されるデジタル画素データのサンプリング位置を調整するデジタルデータ処理部310と、を備え、オフセット部210は、オフセット値を変化させ、デジタルデータ部230は、A/D変換部230から出力されるデジタル画素データのサンプリング位置を、当該デジタル画素データの変化量に基づき調整する。

(もっと読む)

A/D変換装置

【課題】原点基準の入出力特性(入力が0の時に出力も0となる特性)を有するA/D変換装置を提供する。

【解決手段】パルス遅延回路12,13は、入力されるアナログ電圧の大きさに応じた遅延時間でパルス信号を遅延させる遅延ユニットを複数段接続した構成を有する。パルス通過段数検出回路22,23は、パルス信号がパルス遅延回路12,13内の遅延ユニットを通過した段数を検出する。演算出力回路ユニット41は、パルス遅延回路13に対して基準電圧を入力したときにパルス通過段数検出回路23で検出される第1の段数と、パルス遅延回路12に対して、基準電圧にアナログ入力電圧を加算した電圧を入力したときにパルス通過段数検出回路22で検出される第2の段数との差に関する情報を演算し、当該演算の結果を、アナログ入力電圧に対応するデジタル値として出力する。

(もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

オフセット校正回路、オフセット校正方法およびシステム

【課題】 信号に含まれるACオフセットを除去する。

【解決手段】 加算器は、入力信号とオフセットキャンセル信号とを演算し、演算結果を出力信号として出力する。第1極値検出部は、出力信号の信号値のうち正または負の一方を示す複数の極値を求める。第1極大極小検出部は、出力信号に含まれるACオフセットにより変化する一方の極値の第1極大値および第1極小値を求める。第1振幅検出部は、第1極大値および第1極小値の差からACオフセットの第1振幅を求める。第1周期検出部は、第1極大値および第1極小値の一方が現れてから、第1極大値および第1極小値の他方が現れるまでの期間をACオフセットの第1半周期として求める。周期信号生成部は、第1振幅および第1半周期を有する周期信号を生成する。位相調整部は、第1振幅が小さくなる方向に周期信号の位相を調整し、オフセットキャンセル信号として出力する。

(もっと読む)

パイプライン型A/D変換回路

【課題】誤差推定を確実に収束させることができ、比較的短時間で高精度な変換誤差推定及び補正を行うことができる変換誤差補正回路を有するパイプライン型A/D変換回路を提供する。

【解決手段】変換誤差補正回路は、誤差補正対象のサブA/D変換器のサブデジタルコードから、アナログ入力信号と異なる周波数帯域の既知のテスト信号を減算したサブデジタルコードと、誤差補正対象のサブA/D変換器の誤差成分を含む後段のサブA/D変換器のサブデジタルコードとを加算してデジタルコードを生成する演算回路と、演算回路の出力とテスト信号とを乗算する乗算器と、乗算器の出力を長時間平均して、誤差補正対象のサブA/D変換器におけるA/D変換の誤差推定値を算出する長時間平均回路と、その出力を用いて、演算回路から出力されるデジタルコードに含まれるA/D変換の誤差の成分を補正する補正回路とを有する。

(もっと読む)

パイプライン型A/D変換回路

【課題】誤差推定値を算出する時の収束性が非常に高く、比較的短時間で高精度な変換誤差推定及び補正を行うことができる変換誤差補正回路を有するパイプライン型A/D変換回路を提供する。

【解決手段】変換誤差補正回路は、誤差補正対象のサブA/D変換器のサブデジタルコードから既知のテスト信号を減算したサブデジタルコードと、誤差補正対象のサブA/D変換器の誤差成分を含む後段のサブA/D変換器のサブデジタルコードとを加算してデジタルコードを生成する演算回路と、アナログ入力信号をA/D変換する誤差補正用A/D変換器と、演算回路の出力から誤差補正用A/D変換器の出力を減算する減算器と、減算器の出力とテスト信号とを乗算する乗算器と、乗算器の出力を長時間平均して、誤差補正対象のサブA/D変換器におけるA/D変換の誤差推定値を算出する長時間平均回路と、その出力を用いて、演算回路から出力されるデジタルコードに含まれるA/D変換の誤差の成分を補正する補正回路とを有する。

(もっと読む)

161 - 180 / 522

[ Back to top ]