Fターム[5J039DA09]の内容

パルスの操作 (9,993) | 比較要素 (410) | 電圧比較 (400) | FETによるもの(CMOSを除く) (174) | ソースが共通に接続された一対のFETを用いるもの (96)

Fターム[5J039DA09]に分類される特許

1 - 20 / 96

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

インターフェイス回路

【課題】ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現する。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

コンパレータ

【課題】安定したヒステリシス特性を有するコンパレータを提供する。

【解決手段】コンパレータ1は、一対の差動入力トランジスタT1,T2を有する差動回路部10と、差動回路部10にヒステリシスを付加するためのセレクタ回路部20と、レベル変換増幅部30とを備える。セレクタ回路部20は、差動入力トランジスタT1,T2のドレインにそれぞれ接続するトランジスタT3,T4を有し、トランジスタT3,T4の一方がオンするときオンしたトランジスタに接続する側のトランジスタT1,T2から一定のバイアス電流Ibを吸引するように接続される。レベル変換増幅部30の2つの増幅回路31,32は、セレクタ回路部20のトランジスタT3,T4に対して並列に接続されており、差動回路部10の出力に応じてトランジスタT3,T4の一方をオンし同時に他方をオフすることでバイアス電流Ibを切り換える。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

ダイナミック増幅器

【課題】従来のコンパレータは、入力オフセット電圧を高精度に調整することができなかった。

【解決手段】本発明のダイナミック増幅器は、差動対を構成するトランジスタMN1、MN2と、イネーブル状態のリセット制御信号CLKに応じてトランジスタMN1、MN2のドレインの電圧を第1の電圧とするのリセットトランジスタMP5、MP6と、ディスイネーブル状態のリセット制御信号に応じて前記差動対の動作電流を生成する電流源と、トランジスタMN1、MN2のソース間に設けられる抵抗10、11と、トランジスタMN1のソースとトランジスタMN2のソースとの少なくとも一方に接続される容量20、21と、を有し、抵抗10、11の抵抗値及び容量20、21の容量値の少なくとも一方は、オフセット調整信号FL、FRに基づき変更される。

(もっと読む)

半導体集積回路

【課題】差動増幅回路において参照電圧と外部入力信号とを比較する方式を採用した場合においても、出力信号の立ち上がりと立ち下がりとの対称性を維持する。

【解決手段】定電流源回路は、一端が第3及び第4トランジスタのソースである第2ノードに接続され、他端が前記第1電圧とは異なる第2電圧を供給する第2電源ノードに接続される。クランプ回路は、第2ノードと第2電源ノードとの間に電流経路を形成し、第1の外部入力信号が第1の状態から第2の状態に切り替わる場合において、第2ノードを所定の電位に調整する。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

比較回路

【課題】消費電流および回路規模をほとんど増大させることなく、容易に容量の充電時間を短くすることの出来る比較回路を提供する。

【解決手段】差動増幅回路10の出力が入力される単相増幅回路20の出力をNチャネルMOSトランジスタMN5からなるソースフォロワによるクランプ回路41に入力し、当該クランプ回路41により単相増幅回路20の入力を制限することにより、新たに定電圧源を設けることなく必要な充電電圧幅を狭めて容量Cpの充電時間を短くすることができる。また、単相増幅回路10の出力に応じて単相増幅回路10の入力を制限するので、単相増幅回路10の閾値電圧のばらつきや電源電圧の影響が問題にならない。

(もっと読む)

コンパレータのオフセット補正装置

【課題】コンパレータのオフセット補正装置において、ノイズの影響などに起因して、入力しようとしている電圧と実際入力されている電圧との間に差異がある場合にも、正常に閾値オフセット量を補正する。

【解決手段】コンパレータ201のオフセット補正に際しては、開放スイッチ205を開き、短絡スイッチ204を閉じる。この状態において、制御部203はコンパレータ201に対して、2つの入力端子に入力される同一値のリファレンス電圧同士を比較する動作を複数回繰り返させる。フィルタ202は前記複数回の比較結果を平滑化した頻度信号を出力する。前記制御部203は、前記フィルタ202からの頻度信号に基づいて、コンパレータ201での複数回の比較結果のハイレベルとローレベルとの比率が50%になるように、閾値制御信号をコンパレータ201に出力する。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

差動信号受信回路及び半導体装置

【課題】寄生容量を少なくし、動作の高速性を妨げることなく、差動対間のインピーダンスを調整可能にした差動信号受信回路、及び差動信号受信回路を備える半導体装置を提供する。

【解決手段】一対の差動信号が入力する第1、第2の差動トランジスタと、第1、第2の差動トランジスタの出力端子にそれぞれ接続された負荷回路と、第1、第2の差動トランジスタの電源端子に接続された電流源回路と、第1の差動トランジスタの電源端子と前記第2の差動トランジスタの電源端子との間に接続されたインピーダンス調整回路及びスイッチトランジスタと、を備える差動信号受信回路であって、スイッチトランジスタは、差動信号受信回路に供給される電源電圧より高電圧になる信号が印加されて導通、非導通が制御される。

(もっと読む)

A/D変換器

【課題】Tr.補間型比較器列を構成要素とし、プリアンプ列が出力する複数の差電圧を補間しつつAD変換するA/D変換器において、前記Tr.補間型比較器列を構成する複数個のTr.補間型比較器のオフセットをキャンセルする。

【解決手段】複数の抵抗R1〜Rmは複数の参照電圧を発生する。複数のサブ抵抗R11〜Rm4は、前記各参照電圧を更に分解する複数のサブ参照電圧を発生させる。キャリブレーション期間では、キャリブレーション対象となるTr.補間型比較器を選択すると共に、この選択されたTr.補間型比較器の閾値電圧に等しいサブ参照電圧をスイッチSW11〜SWm4により選択し、この選択したサブ参照電圧をスイッチSWAIN1、SWAIN2によりアナログ入力信号AINに代えてプリアンプ列102の各プリアンプA1〜Amに入力し、この状態でキャリブレーションを行う。

(もっと読む)

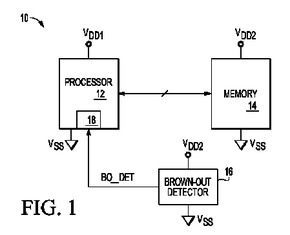

ブラウンアウト検出回路を有するデータ処理システム

ブラウンアウト検出回路(16)は、第1抵抗素子(38)と、第1トランジスタ(46)と、第2トランジスタ(50)と、比較器(40)とを備える。第1抵抗素子(38)が、第1電源電圧端子および第2端子に接続される第1端子を有する。第1トランジスタ(46)は、第1導電性タイプであり、第1抵抗素子(38)の第2端子に接続される第1電流電極と、制御電極と、第2電流電極とを有する。第2トランジスタ(50)は、第2導電性タイプであり、第1トランジスタ(46)の第2電流電極に接続される第1電流電極と、制御電極と、第2電源電圧端子に接続される第2電流電極とを有する。比較器(40)は、第1抵抗素子(38)の第1端子に接続される第1入力端子と、第1抵抗素子(38)の第2端子に接続される第2入力端子と、ブラウンアウト検出信号を供給するための出力端子とを有する。  (もっと読む)

(もっと読む)

コンパレータ及び半導体装置

【課題】動作モードに応じた短い応答時間及び低消費電力と、レイアウト面積の削減とを実現するコンパレータを提供する。

【解決手段】コンパレータは、第1の動作モードに対応した第1の電圧と、第2の動作モードに対応した第1の電圧より低い第2の電圧とのいずれか一方を基準電圧として選択される動作モードに応じて出力する基準電圧生成回路と、第1の動作モードに対応した第1の定電流と、第2の動作モードに対応した第1の定電流より低い第2の定電流とのいずれか一方を選択される動作モードに応じて供給する定電流回路と、定電流回路により電流が供給され、外部から入力される電圧と基準電圧生成回路が出力する基準電圧とを比較した比較結果を出力する差動増幅回路とを備え、差動増幅回路が出力する比較結果に応じて、第1及び第2の動作モードのいずれか一方が動作モードに選択される。

(もっと読む)

1 - 20 / 96

[ Back to top ]