Fターム[5J039JJ07]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318) | 間隔、位置 (257) | 位相 (245)

Fターム[5J039JJ07]の下位に属するFターム

位相及び周波数 (33)

2入力が複数倍以上周期の異なるもの (2)

Fターム[5J039JJ07]に分類される特許

61 - 80 / 210

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

位相検出回路およびPLL回路

【課題】2つのクロック信号の位相比較に基づき生成する2つのパルス信号の遅延時間を極力短くすることができ、かつ確実にリセットできる位相検出回路および該位相検出回路を備えたPLL回路を提供すること。

【解決手段】位相検出回路は、位相比較を行う2つのクロック信号の論理和信号と論理積信号とに基づき、進相側と遅相側の2つのパルス信号の生成に用いる一方の出力を、前記位相比較を行う準備動作状態と、前記位相比較を行った回路動作状態とに切り替えて保持するラッチ回路を備えている。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

半導体装置

【課題】高速の半導体装置で要求されるクロック整列トレーニング動作を提供すること。

【解決手段】システムクロック及びデータクロックを入力されるクロック入力部(200)と、データクロックの周波数を分周して所定の位相差を有する複数の多重位相データ分周クロックを生成し、分周制御信号に応答して多重位相データ分周クロックの位相の反転可否を決定するクロック分周部(220)と、多重位相データ分周クロックのうち所定の第1選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応して分周制御信号のレベルを決定する第1位相検出部(240)と、多重位相データ分周クロックのうち所定の第2選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応してトレーニング情報信号を生成する第2位相検出部(260)と、トレーニング情報信号を外部に伝送するための信号伝送部(270)とを具備する。

(もっと読む)

半導体装置及び位相検知回路

【課題】位相検知の誤判定を防止した高精度の位相検知回路を提供する。

【解決手段】電源線VSS1とセンスノードLSAT、LSAB間に、nMOSトランジスタの組(M1、M2、M3)、(M4、M5、M6)を備え、各トランジスタのゲートに内部クロックRCLK、RCLKのインバータINV1による反転信号、外部ロックCK、/CKをそれぞれ入力し、電源線VDD1とセンスノードLSAT、LSAB間に、pMOSトランジスタの組(MP1、MP2、MP3)、(MP4、MP5、MP6)を備え、各トランジスタのゲートにFCLKのインバータINV2による反転信号、内部クロックRCLK、外部ロックCK、/CKをそれぞれ入力し、センスノードLSAT、LSABは差動アンプAMPで増幅されラッチ回路L1でラッチされる。pMOSトランジスタ(MP11、MP12、MP13)はLSAT、LSABをプリチャージ・イコライズする。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

位相比較器及びその位相比較器を用いたクロック・リカバリ回路

【課題】

クロックによりサンプリングされた受信データ間のゼロクロス点の位相を高精度で検出することが可能な位相検出器を提供することである。

【解決手段】

第1受信データの第1データ値及び第2受信データの第2データ値に対応した論理を備える判別信号を発生するタイミング判別器と、第1受信データのサンプリング時刻及び第1データ値と、第2受信データのサンプリング時刻及び第2データ値とから補間計算により求めらる、第1ゼロクロス時刻とクロックとの位相関係に関する第1位相情報を抽出する第1ゼロクロス抽出器と、第1データ値及び第1受信データのサンプリング時刻に基づいて、単位時間当たりのデータ値の増分を用いて求められた、第2ゼロクロス時刻とクロックとの位相関係に関する第2位相情報を抽出する第2ゼロクロス抽出器と、判別信号の論理に対応して、第1位相情報又は第2位相情報の内の一方を選択するセレクタと、を備える位相比較器。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

遅延比較回路、遅延比較方法、遅延回路および半導体集積回路

【課題】複数の遅延回路における遅延差(位相差)を高精度で比較することができる遅延比較回路の提供を図る。

【解決手段】複数のディレイライン1,2と、該各ディレイラインをそれぞれオシレータ化する複数のオシレータ補助回路6,8;7,9と、オシレータ化された前記各ディレイラインの発振出力をカウントしてそれぞれカウント値を求める複数のカウンタ3,4と、前記各カウント値を基準カウント値と比較する比較部5と、を有するように構成する。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

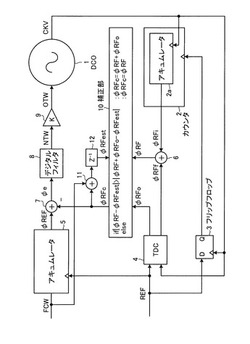

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

61 - 80 / 210

[ Back to top ]