Fターム[5J039JJ07]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318) | 間隔、位置 (257) | 位相 (245)

Fターム[5J039JJ07]の下位に属するFターム

位相及び周波数 (33)

2入力が複数倍以上周期の異なるもの (2)

Fターム[5J039JJ07]に分類される特許

81 - 100 / 210

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

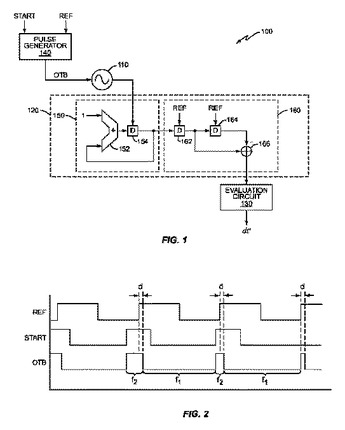

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

位相比較装置

【課題】高速動作するBang-Bang型位相比較回路の出力パルスに歪や欠損がある場合であっても、チャージポンプやA/D変換器を用いることなく、進相、遅相のいずれであるかを正確に表すデジタル信号を得る。

【解決手段】Bang-Bang型の位相比較回路10と、該位相比較回路の進相出力パルスおよび遅相出力パルスを入力して遅相/進相の識別を行う位相比較結果識別回路20とを備える。位相比較結果識別回路20は、位相比較回路10の進相出力パルスによってリセットされた後にクロック信号のカウントを行い所定のカウント値に達すると遅相を示す信号を出力する第1カウンタ回路21と、位相比較回路10の遅相出力パルスによってリセットされた後に前記クロック信号のカウントを行い所定のカウント値に達すると進相を示す信号を出力する第2カウンタ回路22と、前記遅相を示す信号と前記進相を示す信号を入力して進相/遅相の識別信号を出力する識別回路23とを具備する。

(もっと読む)

信号処理装置

【課題】 温度によるクロックの変動を抑える。

【解決手段】 クロックを用いて信号を生成する信号処理部と、外部からの入力信号と前記信号処理部から出力された信号との位相差を検出し、前記位相差を示す信号を出力すると共に前記入力信号が無くなるとその直前の位相差の信号を出力する位相差検出部と、温度補償型の発振器からの出力信号に応じて前記位相差検出部からの出力に応じた値をカウントし、前記カウント値に基づいて基準信号を生成するデジタル発振器と、前記デジタル発振器からの基準信号と前記クロックを分周した信号との位相差に応じて前記クロックを生成するクロック生成部とを備える。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

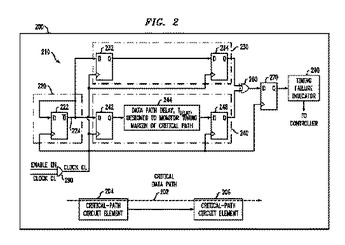

性能監視用クリティカルパス回路

目標タイミング・マージンを有する、クリティカルパス中のタイミングを監視する監視回路を含む集積回路が、開示される。監視回路は、2つのシフト・レジスタを含み、シフト・レジスタの1つは、受領信号に遅延値を加える遅延素子を含む。2つのシフト・レジスタの入力部は、入力信号を受領することができる信号入力ノードを形成する。監視回路は、出力部および少なくとも2つの入力部を有する論理ゲートも含み、各入力部は、2つのシフト・レジスタの出力部の対応する1つに接続される。論理ゲートの出力部は、目標タイミング・マージンが満足されるか、または満足されないかを示す。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

データ復元回路、データ復元方法、及びデータ受信装置

【課題】安定した動作を容易に実現することができるデータ復元回路を提供する。

【解決手段】データ復元回路は、データ列を表す入力アナログ信号をクロック信号に同期してアナログデジタル変換することにより、前記データ列のデータ間隔より短い間隔でサンプルしたデジタルコードの列を生成するアナログデジタル変換器と、前記デジタルコードが値を取り得る範囲の略中心にある所定のコード値の位置と前記デジタルコードの列を補間して得られる線分とが交差するクロス点の位置を前記デジタルコードの列から算出する位相検出器と、前記クロス点の位置に基づいて前記データ列のデータ中心点の推定位置を求める位相推定器と、前記クロス点の位置と前記データ中心点の推定位置とに基づいて前記デジタルコードの列からデータ判定値の列を抽出するデータ判定部とを含む。

(もっと読む)

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

81 - 100 / 210

[ Back to top ]